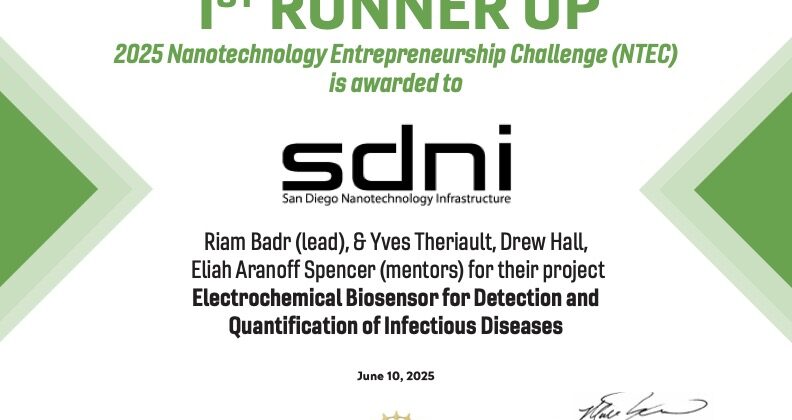

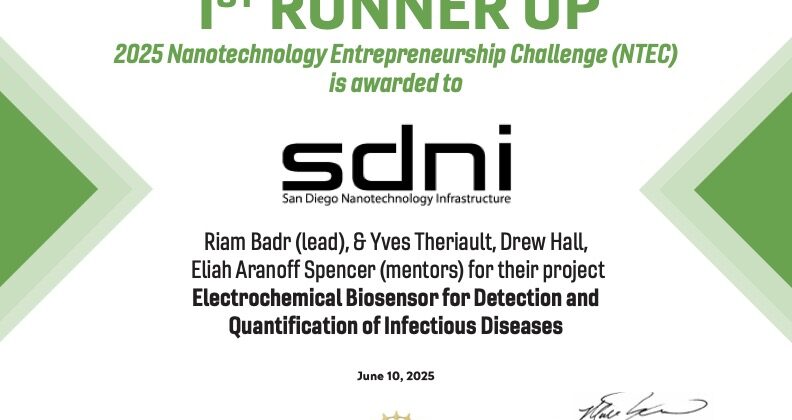

Riam was the runner-up in the NSF-sponsored Nanotechnology Entrepreneurship Challenge (NTEC) for her work on “Electrochemical Biosensor for Detection and Quantification of Infectious Diseases.”

Riam was the runner-up in the NSF-sponsored Nanotechnology Entrepreneurship Challenge (NTEC) for her work on “Electrochemical Biosensor for Detection and Quantification of Infectious Diseases.”

Asish was voted the runner up for the poster presentation award at the Center for Wearable System Fall Symposium! Asish presented his work on impedance-based blood clotting time measurement. Congratulations, Asish!

I am pleased to share that my (now former) student, Dr. Corentin Pochet, received the 2023-2024 Dr. William S.C. Chang Best Dissertation Award for his thesis titled “Higher-order VCO-based ADCs for Sensor Interfaces!” In his thesis, Corentin describes several innovations at the circuit and architecture level that can increase the noise-shaping order of a VCO-based ADC and achieve outstanding linearity. These techniques are implemented in two chips that he taped out.

The first ADC was designed to interface directly with high-impedance recording electrodes and provide a wide dynamic range and linearity to absorb motion artifacts and correct them in the digital domain. The prototype ADC achieves 2nd-order noise-shaping with high linearity and power efficiency using a novel gated inverted ring oscillator (GIRO)-based time-to-digital converter and a multi-quantizer scheme. The ADC achieves a dynamic range greater than 90 dB and above 110 dB of linearity while consuming only 5.4 µW of power! This was published in ISSCC and subsequently invited to TBioCAS.

The second prototype was developed by building upon the feedforwarding techniques commonly used in the standard voltage domain ADC architectures and applying them to capacitively coupled VCO-based ADCs. Using the pseudo-virtual ground (PVG) at the input of the VCO integrator and feeding it further down the loop, he showed that high linearity and higher-order noise-shaping shaping could be achieved extremely power-efficiently. The prototype achieved 3rd-order noise-shaping with a 92.1 dB SNDR and a peak linearity of 123 dB while consuming only 4.4 µW. This led to a Schreier FoM of 179.6 dB, indicating how efficient the proposed structure is and showing comparable performance to standard voltage domain architectures. This was published in ISSCC and subsequently invited to JSSC.

To better contextualize his work, I refer you to the plots below. These plots show the landscape of ADC performance over the past 25+ years, comparing the Schreier FoM versus the conversion rate (fs,nyq) of the ADC, where a higher FoM indicates higher performance. When Corentin started his PhD, there was a 20 dB gap between the best-performing voltage-mode ADCs and the best VCO-based ADCs. Throughout his thesis, he closed this gap to less than 4 dB and (shhh….) recently taped out a chip that is even better than all voltage-mode ADCs. Corentin’s works are circled.

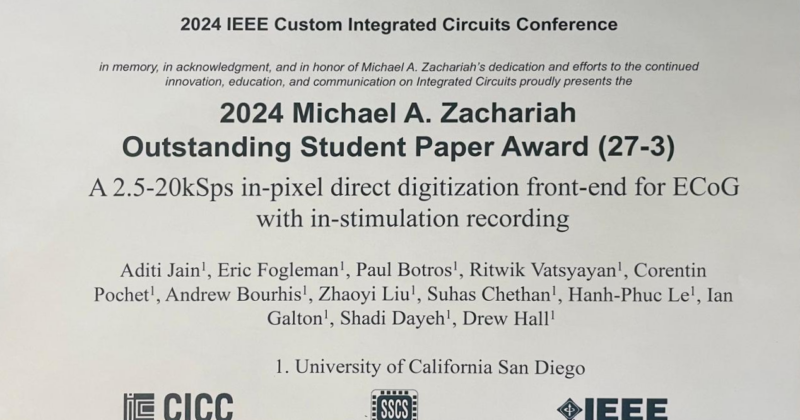

Aditi presented her work on a VCO-based neural recording front-end that is stimulation artifact tolerant at the IEEE Custom Integrated Circuits Conference (CICC) in Denver last week. I’m happy to report that the paper won the conference’s Outstanding Student Paper Award! Congratulations, Aditi! Read the paper here.

Omid successfully defended his thesis titled “The Role of CMOS-Enabled Biomedical Devices in Digital Healthcare: from Real-time in-vivo Wireless Sensor Nodes to Biomarker Probe Synthesis.” Omid shared two exciting, highly innovative projects using CMOS chips for electrochemistry. The first, BioMote, is a sub-uW, fully self-contained injectable sensor for continuous analyte monitoring, and the second is a high-density DNA synthesis platform. He has a very impressive body of work, and we wish him all the best in his future endeavors. Congratulations, Dr. Ghadami!

As has become a tradition in our research group, we celebrated with a chip cake.

It was a big day — Michael successfully defended his thesis titled “Magnetic Biosensors for Immunoassays and Enzymatic Activity Quantification,” and Michael’s first first-author paper was accepted! Michael shared two assays he developed based on giant magnetoresistive (GMR) sensors. The first quantifies two biomarkers relevant to spontaneous preterm birth (link), and the second demonstrates the versatility of real-time enzyme-based release assays. We wish him all the best in his future endeavors. Congratulations, Dr. Sveiven!

As has become a tradition in our research group, we celebrated with a chip cake.

Corentin successfully defended his thesis titled “Higher-order VCO-based ADCs for sensor interfaces” today. Over the past 6 years, Corentin showed that VCO-based ADCs could achieve performance commiserate with their voltage-mode counterparts. A very impressive body of work, and we wish him all the best in his future endeavors. Congratulations, Dr. Pochet!

As has become a tradition in our research group, we celebrated with a chip cake.

Corentin will present his work titled “A 4.4µW, 2.5kHz-BW, 92.1dB-SNDR 3rd-Order VCO-based ADC with Pseudo Virtual Ground Feedforward Linearization” at ISSCC this year! This work shows how one can feed forward the pseudo virtual ground in a capacitively coupled VCO-based ADC to linearize and stabilize the system while only using a single feedback DAC. This approach enables a high dynamic range (DR) due to the 3rd-order noise-shaping and >120dB SFDR due to the linearization. The prototype ADC consumes 4.4µW from a 0.8V supply achieving the best-reported SNDR Schreier Figure-of-Merit (FoM) for VCO-based ADCs at 179.6dB.

Congratulations, Corentin!

Congratulations, Dr. Ying! Da successfully defended his thesis on electrochemical biosensor front-ends. Da will join Apple soon.