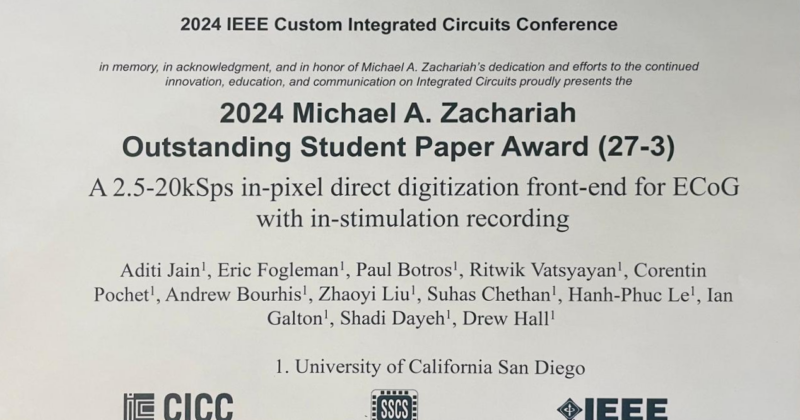

I am pleased to share that my (now former) student, Dr. Corentin Pochet, received the 2023-2024 Dr. William S.C. Chang Best Dissertation Award for his thesis titled “Higher-order VCO-based ADCs for Sensor Interfaces!” In his thesis, Corentin describes several innovations at the circuit and architecture level that can increase the noise-shaping order of a VCO-based ADC and achieve outstanding linearity. These techniques are implemented in two chips that he taped out.

The first ADC was designed to interface directly with high-impedance recording electrodes and provide a wide dynamic range and linearity to absorb motion artifacts and correct them in the digital domain. The prototype ADC achieves 2nd-order noise-shaping with high linearity and power efficiency using a novel gated inverted ring oscillator (GIRO)-based time-to-digital converter and a multi-quantizer scheme. The ADC achieves a dynamic range greater than 90 dB and above 110 dB of linearity while consuming only 5.4 µW of power! This was published in ISSCC and subsequently invited to TBioCAS.

The second prototype was developed by building upon the feedforwarding techniques commonly used in the standard voltage domain ADC architectures and applying them to capacitively coupled VCO-based ADCs. Using the pseudo-virtual ground (PVG) at the input of the VCO integrator and feeding it further down the loop, he showed that high linearity and higher-order noise-shaping shaping could be achieved extremely power-efficiently. The prototype achieved 3rd-order noise-shaping with a 92.1 dB SNDR and a peak linearity of 123 dB while consuming only 4.4 µW. This led to a Schreier FoM of 179.6 dB, indicating how efficient the proposed structure is and showing comparable performance to standard voltage domain architectures. This was published in ISSCC and subsequently invited to JSSC.

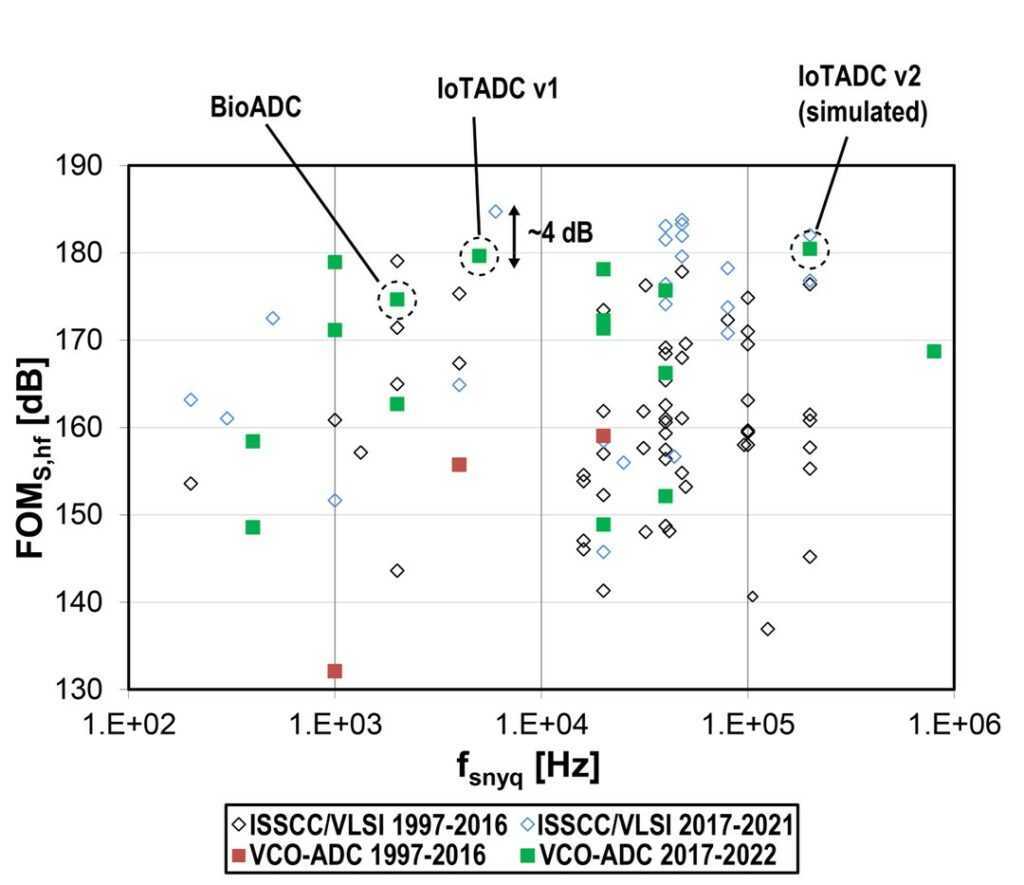

To better contextualize his work, I refer you to the plots below. These plots show the landscape of ADC performance over the past 25+ years, comparing the Schreier FoM versus the conversion rate (fs,nyq) of the ADC, where a higher FoM indicates higher performance. When Corentin started his PhD, there was a 20 dB gap between the best-performing voltage-mode ADCs and the best VCO-based ADCs. Throughout his thesis, he closed this gap to less than 4 dB and (shhh….) recently taped out a chip that is even better than all voltage-mode ADCs. Corentin’s works are circled.