The National Science Foundation (NSF) funded our proposal to develop a pandemic preparedness framework. Look forward to working with the many collaborators at UCSD on this project led by Dr. Aronoff-Spencer. Read more about it here.

Omid to present at VLSI 2022

I am excited to report that our paper, “Helix: An Electrochemical CMOS DNA Synthesizer,” will be presented tomorrow at VLSI in Honolulu by Omid! This was a multi-year collaborative effort with Avery Digital to demonstrate high-density DNA synthesis atop a CMOS chip. We developed a new low-voltage redox chemistry, implemented post-processing techniques for high-density platinum electrodes (as small as 0.6μm2), and synthesized oligos up to 100 nucleotides. Come check out the exciting talk!

Congratulations, Dr. Pochet!

Corentin successfully defended his thesis titled “Higher-order VCO-based ADCs for sensor interfaces” today. Over the past 6 years, Corentin showed that VCO-based ADCs could achieve performance commiserate with their voltage-mode counterparts. A very impressive body of work, and we wish him all the best in his future endeavors. Congratulations, Dr. Pochet!

As has become a tradition in our research group, we celebrated with a chip cake.

Corentin to present at ISSCC 2022

Corentin will present his work titled “A 4.4µW, 2.5kHz-BW, 92.1dB-SNDR 3rd-Order VCO-based ADC with Pseudo Virtual Ground Feedforward Linearization” at ISSCC this year! This work shows how one can feed forward the pseudo virtual ground in a capacitively coupled VCO-based ADC to linearize and stabilize the system while only using a single feedback DAC. This approach enables a high dynamic range (DR) due to the 3rd-order noise-shaping and >120dB SFDR due to the linearization. The prototype ADC consumes 4.4µW from a 0.8V supply achieving the best-reported SNDR Schreier Figure-of-Merit (FoM) for VCO-based ADCs at 179.6dB.

Congratulations, Corentin!

Congratulations, Corentin!

Corentin was awarded an IEEE SSCS Predoctoral Achievement Award. Congratulations, Corentin! Check out some of Corentin’s IC work: JSSC’20, ISSCC’21, ISCAS’21, JSSC’21, TCAS2’21, and TBioCAS’21. The award will be presented virtually at ISSCC this year. Read more about Corentin and the other winners here.

Congratulations, Dr. Ying

Congratulations, Dr. Ying! Da successfully defended his thesis on electrochemical biosensor front-ends. Da will join Apple soon.

Prof. Hall giving talk at Nature Nano – Next Generation of Sensors on Mar 24th

I will be giving an invited talk on our COVID-19 work at the event “Nano – Next Generation of Sensors” put on by the Springer Nature group. This event will cover technologies for “Cutting Edge (Bio)Sensing Technologies for Fighting Infectious Diseases.” Registration is free (link).

Corentin to present at ISSCC 2021

Come check out our ISSCC paper, #28.4 titled “A 400mVpp 92.3dB-SNDR 1kHz-BW 2nd-Order VCO-Based ExG-to-Digital Front-End Using a Multiphase Gated-Inverted Ring-Oscillator Quantizer.” Corentin will describe a second-order VCO-only delta-sigma ADC with a wide dynamic range (>90dB) and a high input impedance (>50MΩ) enabling the direct digitization of ExG signals even in the presence of large motion artifacts while consuming less than 6μW. Great work from Corentin Pochet, Jiannan(Jason) Huang, and Patrick Mercier!

Somok to present at ISSCC 2021

Come check out our ISSCC paper, #10.2 titled “A 139μW 104.8dB-DR 24kHz-BW CTΔΣM with Chopped AC-Coupled OTA-Stacking and FIR DACs”. Somok will present our work on “OTA-Stacking” to improve the noise efficiency of circuits. Having already shown the benefit of this technique in an ultra-low power ECG amplifier, we demonstrate how this can be used in an analog-to-digital converter (ADC) with state-of-the-art performance. Congrats, Somok Mondal and Omid Ghadami! Also, a post on the JSOE blog here.

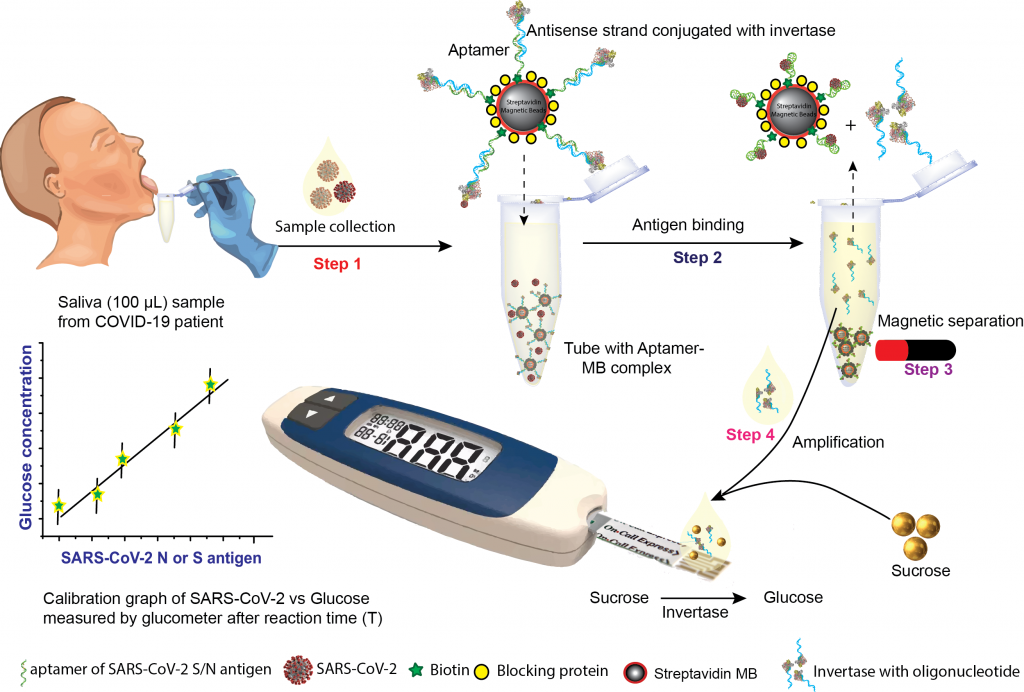

Rapid CoVID-19 Antigen Test Funded

Our rapid CoVID-19 saliva-based test using an off-the-shelf glucometer was recently funded by the National Institutes of Health (NIH) under the Rapid Acceleration of Diagnostics (RADx) program. Read more about our exciting work here.