# Integrated Circuits for Wireless Communications: Research Activities at the University of California, San Diego

Peter Asbeck<sup>®</sup>, Dinesh Bharadia<sup>®</sup>, Ian Galton, Drew Hall<sup>®</sup>, Hanh-Phuc Le<sup>®</sup>, Patrick Mercier<sup>®</sup>, and Gabriel Rebeiz

he continuing demand for improved wireless connectivity and enhanced data rates has spurred worldwide research in microwave and millimeter (mm)-wave circuits and systems within academia, government, and industrial centers. At the University of California, San Diego (UCSD), the Center for Wireless Communications (CWC) was established more than two decades ago and has contributed to analog, microwave, and millimeter circuits and systems research; communication and information theory; coding; and application studies for 4G, 5G, and 6G wireless systems. This article highlights recent UCSD research efforts, emphasizing the microwave and mm-wave circuits and systems and accompanying analog circuit techniques, carried out in conjunction with the CWC.

Multiple companies from around the world have sponsored UCSD research, and additional research has been funded through numerous U.S. government awards. The closeness between the wireless industry

Peter Asbeck (asbeck@ece.ucsd.edu), Dinesh Bharadia (dineshb@eng.ucsd.edu), Ian Galton (galton@eng.ucsd.edu), Drew Hall (dahall@eng.ucsd.edu), Hanh-Phuc Le (hanhphuc@eng.ucsd.edu), Patrick Mercier (pmercier@eng.ucsd.edu), and Gabriel Rebeiz (rebeiz@ece.ucsd.edu) are with the Department of Electrical and Computer Engineering, University of California, San Diego, La Jolla, CA 92093 USA.

Digital Object Identifier 10.1109/MMM.2023.3240535

Date of current version: 6 April 2023

firms and the university has been particularly valuable in focusing the research on themes important for applications. Graduates of the program have also had a major influence on wireless industry activities, particularly in California.

This article first covers research results in mm-wave circuits and assemblies for antenna array transmitters and receivers for 5G and beyond, followed by a discussion of low-power microwave circuits for Internet of Things (IoT) applications, mixed-signal circuits for translating the relevant signals between microwave and digital domains, and a novel system methodology for interfacing with low-power wireless nodes via Wi-Fi.

# mm-Wave Antenna Array Transmitters and Receivers

A cornerstone of wireless communication systems at high frequencies is the use of antenna arrays to direct the transmitted power toward the desired receiver (or multiple receivers) in appropriate narrow beams. As the number of elements in the array increases, the beamwidth decreases, enabling efficient focusing of the output power on the desired receivers. For large arrays, it is a significant challenge to provision

appropriately phased and amplitude-controlled signals to the different array elements, which are typically spaced at distances of half the free space wavelength of the carrier frequency. Prof. Gabriel Rebeiz's group has been pioneering the development of affordable satellite communications (SATCOM) and 5G phased arrays based on silicon technologies since 2005 [1], [2], [3], [4], [5], [6], [7], [8, and references therein]. At present, these systems can integrate the entire phased array on a single low-cost printed circuit board that includes the antennas, silicon beamformer chips, and the necessary control electronics. The board can be assembled using automated high-volume manufacturing techniques, making it very low cost in large numbers, and is also calibrated using built-in tests and also fast far-field pattern measurements. UCSD and Rebeiz's group pioneered this approach for phased arrays and developed the first silicon phased array chips (called beamformer chips) based on the 2 × 2 quad approach and the first single-printed circuit board (PCB) phased arrays. This has lowered the cost of phased arrays by a factor of 50-100×, making them affordable for commercial use in SATCOM and mm-wave 5G. A representative example is shown in Figure 1, a 1,024-element receiver array

May 2023 IEEE microwave magazine 3

covering the K-band (17.7–20.2 GHz) for SATCOM [7]. A single PCB of 25 cm  $\times$  22 cm is used, making it the largest single-PCB K-band array to date. The narrow 3.5° beamwidth with  $\pm 70^{\circ}$  scan angles enables tracking satellites in low Earth orbit, an emerging area for broadband connectivity.

The same ideas and techniques have been used by companies such as SpaceX/Starlink for their SATCOM terminals (known as "Dishy"), Collins Aerospace, Viasat, Boeing, and others for their airborne phased array terminals on commercial and defense aircraft and Qualcomm, Nokia, Samsung, Ericsson, and several other companies for their low-cost 5G phased arrays at 28 GHz and 39 GHz. It is no exaggeration that

every affordable phased array built today follows the silicon beamformers and single-PCB design approach developed at UCSD.

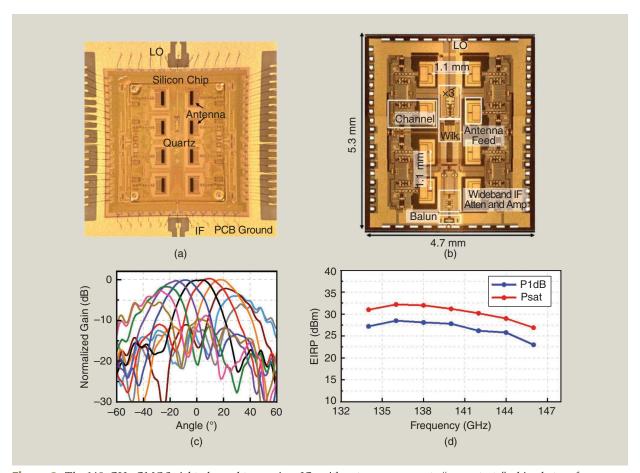

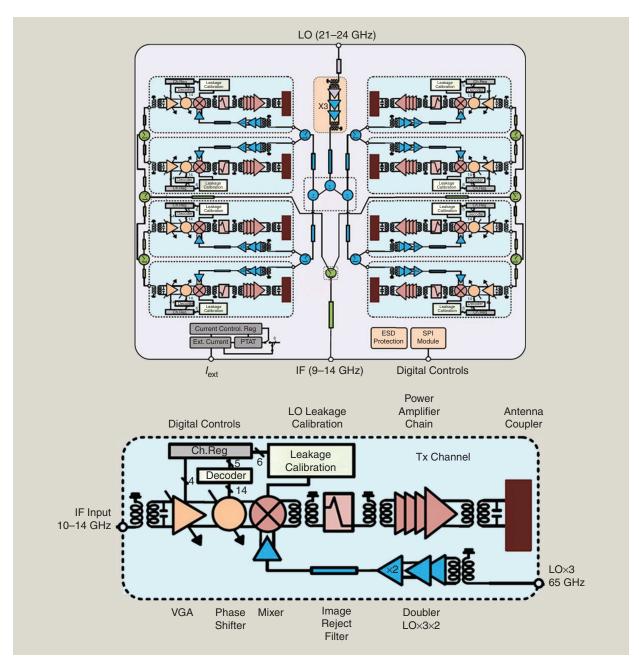

Prof. Rebeiz continues developing wideband phased arrays for X-/Ku-/Ka-band SATCOM, 18- to 50-GHz wideband 5G systems, and 140-GHz 6G phased arrays. His group has also developed large wafer-scale phased arrays for mm-wave applications and proven them at 60 GHz, 110 GHz, and 140 GHz. For example, for potential applications in 6G, an eight-channel transmit array and an accompanying eight-channel receive array were demonstrated using Si CMOS-silicon on insulator (SOI) technology, shown in Figure 2 [6], [8]. Antennas were directly mounted on top of the Si ICs, using metal

**Figure 1.** The 1,024 dual-polarized phased array for K-band SATCOM. (a) A PCB photograph illustrating electronic side and patch antenna side. (b) The output pattern for broadside emission showing 3.5° beamwidth, cross-polarization, and simulation. (c) The antenna patterns covering scan angles of  $\pm 80^\circ$ .

32

patterns on a quartz plate; the tight integration was made possible by the small 1-mm distance between antennas. Local oscillator (LO) routing around the chip was done at a subharmonic, and upconversion to 140 GHz was carried out at each channel, as shown in Figure 3. Prof. Rebeiz and his former students founded Extreme Waves, a company in San Diego developing and delivering phased arrays for SATCOM, 5G, and specialized functions.

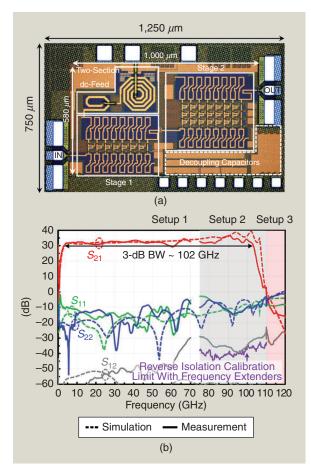

In addition to phased arrays, the Rebeiz group has demonstrated a variety of key building block circuits for high-frequency systems, including power amplifiers (PAs) (as detailed in the section below), LNAs, phase shifters, filters, and voltage-controlled oscillators. Another ground-breaking circuit for instrumentation and optical communication applications is a distributed amplifier with over 100 GHz bandwidth, 33 dB gain, and peak output power of 23 dBm, shown in Figure 4 [9].

## Microwave and mm-Wave PAs

The overall range and efficiency of wireless transmitters are typically determined by the PA; accordingly, PAs have been the topic of intensive research. For mm-wave communications (notably 5G), the use of antenna arrays and the resultant spatial power combining has meant that peak output power in the neighborhood of 20 dBm is adequate to provision a given antenna, and this is in the realm of what be achieved with Si technology. Bulk CMOS, CMOS-SOI, and SiGe HBT are all candidates for use in both handsets and base stations, along with GaN PAs for very high power transmitters. Efficiency is a central concern, which is exacerbated by the fact that amplifiers must operate in backoff due to the high peak-to-average power ratio for the signals, typically 8-9 dB. Linearity requirements provide an additional challenge: while at microwave frequencies, digital predistortion is typically used to mitigate PA nonlinearity; for the mm-wave antenna arrays with large numbers of individual PAs and wide bandwidth requirements (200 to 1,000 MHz), the PA intrinsic linearity must be sufficient to amplify signals with error vector magnitude down to 3-5%.

A primary focus of 5G and 6G PA research at UCSD has been CMOS-SOI, which provides a variety of advantages. Excellent isolation between devices facilitates series-connecting FETs ("stacking") to enhance

**Figure 2.** The 140-GHz CMOS eight-channel transceiver ICs with antennas on quartz "superstrate": chip photos of (a) transmitter and (b) receiver and (c) and (d) measured transmitter performances. EIRP: equivalent isotropically radiated power.

their voltage-handling capability. The buried oxide decreases the parasitic capacitance to the substrate. In the GlobalFoundries 45-nm CMOS-SOI technology, high-resistivity (>1,000 ohm-cm) Si substrates are used, virtually eliminating capacitance of interconnect lines to the substrate. High figures of merit ft and fmax in the vicinity of 300–400 GHz are also obtainable.

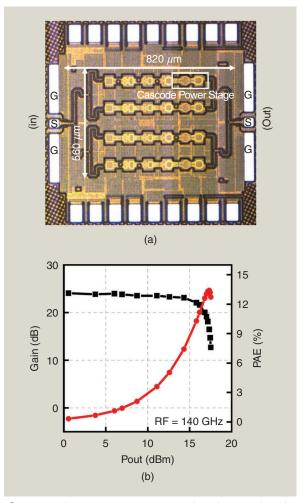

In conjunction with the 6G-oriented transceiver at 140 GHz described previously, Prof. Rebeiz's group demonstrated a ground-breaking Si 45-nm CMOS-SOI PA for use at 130–150GHz, showing the potential of

Si-only technology for practical use in wireless transmitters above 100 GHz [10]. As shown in Figure 5, the four-stage PA achieves a saturated output power of 17.5 dBm and an efficiency of 13% at 140 GHz.

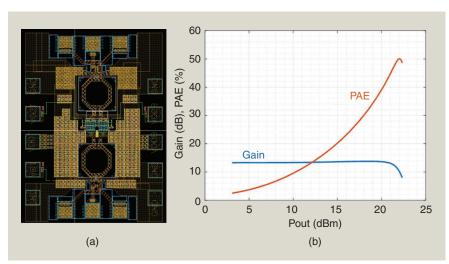

One target of UCSD's research for mm-wave 5G (24–40 GHz) has been demonstrating high power and efficiency. With the use of pMOS rather than nMOS, in Asbeck's group, power-added efficiency (PAE) up to 50% and output power up to 22 dBm have been demonstrated in a simple two-stack differential amplifier [11], as shown in Figure 6. The use of pMOS enables

**Figure 3.** The anatomy of a 140-GHz phased array transmitter IC. To avoid the necessity of routing 140-GHz signals all around the  $5.4 \times 5.1 \text{ mm}^2$  chip, a lower-frequency LO is fed in and multiplied  $\times 6$  prior to mixing with the IF. Beamforming is done at IF. An image reject filter is used in each channel. VGA: variable gain amplifier.

IEEE microwave magazine

increasing the power supply voltage without sacrificing reliability, because of superior resistance to hot carrier injection and increased ability to handle high voltage when the device is off (in class B or deep class AB operation). The PA uses only a positive supply (connected to the source) to maintain compatibility with conventional nMOS circuits.

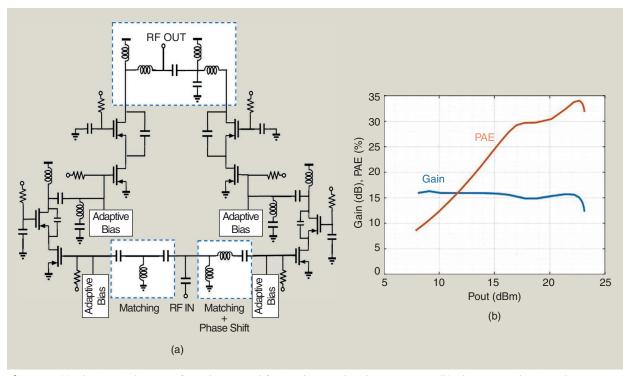

Another target of research has been to provide high efficiency in backoff. Doherty amplifiers have been implemented in nMOS-SOI and pMOS-SOI, using lowloss output impedance matching and power combining designed using the Ozen technique [12], [13], [14]. Figure 7 illustrates the circuit diagram for a pMOS Doherty, which achieves 20% PAE at 8 dB backoff from the saturated output power of 23.5 dBm at 27 GHz. It is notoriously difficult to maintain good linearity in a Doherty PA; digital predistortion is almost always used in the microwave frequency range. Here good linearity is achieved with multiple active bias networks that detect the transmitted power on the chip with FETbased rectifiers and adjust the gain by controlling gate biases accordingly. In high-frequency Doherty amplifiers, this is particularly valuable to facilitate a transition

**Figure 4.** The broadband high-power distributed amplifier in 45-nm CMOS-SOI: chip layout and measured characteristics.

for the peaking amplifier from deep class C to class AB as the input power increases, without sacrificing gain. The active bias networks are also used to mitigate soft saturation effects in amplifier AM–AM characteristics.

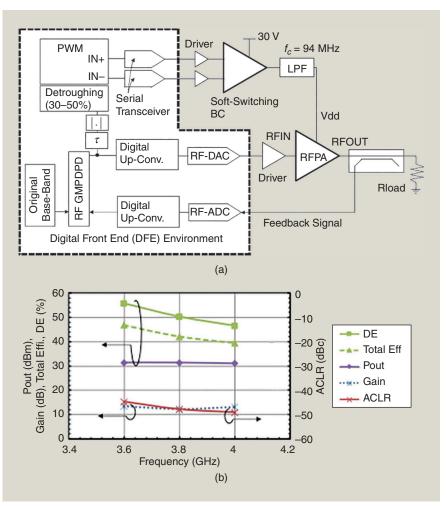

Improved efficiency at backoff can also be achieved using envelope tracking (ET). This technique, based on the use of a dynamically varied power supply voltage, has been the subject of extensive past development at UCSD for base station and handset applications at 1-2 GHz [15], [16] and is now in use in many smartphones. ET research is continuing with a primary focus on base station applications for 4G and 5G in sub-6-GHz bands. One novel theme being explored by Prof. Hanh-Phuc Le's research group is based on a multiple switched capacitor network [17], [18] to supply a menu of fixed supply voltages to a GaN base station 5G-NR PA, allowing it to select the most efficient voltage on a symbol-by-symbol basis [19]. Another recent result is a tour-de-force ET amplifier system achieved by collaborative industry-CWC research (led by Mitsubishi Electric and Nokia/Bell Labs). A 3.6- to 4.0-GHz ET

**Figure 5.** The 140-GHz CMOS PA: chip photograph and performance characteristics. PAE: power-added efficiency.

amplifier was demonstrated using a GaN soft-switching buck converter feeding a GaN 0.15-µm HEMT PA, in conjunction with a digital front-end environment for signal generation and predistortion [20]. ACLR was below -45 dBc, and total efficiency reached 47% at 3.6 GHz, as shown in Figure 8.

# **IoT: Wake-Up Receivers**

36

Most IoT devices require RFICs to communicate information among each other and/or with local infrastructure.

**Figure 6.** (a) The layout of differential pMOS-SOI Ka-band amplifier using positive supply voltage. (b) The measured gain and PAE at 25 GHz versus output power.

Many of these devices use wireless standards such as Bluetooth Low Energy, Wi-Fi, Zigbee, LoRa, NB-IoT, etc.; however, these standards were designed to support high throughput, from tens of kbps to tens of Mb/s. As such, the power consumption of these devices is commensurately high, or they lower power by turning off the radios for extended periods, lengthening the latency of connecting the device to the network. However, many emerging IoT applications do not require high average throughput: consider, for example, appli-

cations in perimeter detection or infrastructure monitoring, where communication is not needed until relatively infrequent events occur. Unfortunately, most radio standards require frequent packet communication for network synchronization purposes, even if there are no data to transmit. This stay-on-to-communicate approach can reduce battery life significantly [21], [22].

Wake-up receivers (WuRXs) provide an elegant solution by continuously monitoring the RF spectrum for prespecified event signatures (i.e., wake-up messages) that tell the WuRX to

**Figure 7.** (a) The circuit diagram of a Doherty amplifier implemented with pMOS-SOI. (b) The measured gain and PAE at 27 GHz versus output power.

enable the device to take further action, such as turning on the main radio. If a wakeup event is detected, the normal main radio can provide high-throughput communication without requiring frequent synchronization packet communication. The WuRX provides energy savings if its average power consumption is lower than the power of the main radio at the target latency for device response to a query over the network. For many standards-based radios, the target latency is imposed by the standard or by an application-dependent communication latency constraint. If the active WuRX power consumption is low, the energy savings can be substantial.

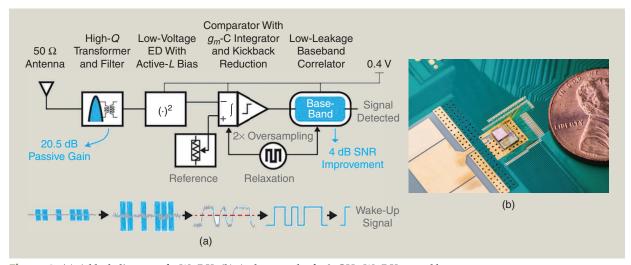

With support from the Defense Advanced Research Projects Agency, researchers in the groups of Prof. Drew Hall, Patrick Mercier, and Gabriel Rebeiz developed several WuRXs with nanowatt-level power consumption, less than the leakage power of a coin

cell battery. The first radio demonstrated a 113.5-MHz OOK-modulated WuRX that achieved –69 dBm sensitivity with only 4.5 nW, as shown in Figure 9(a) [22], [23], [24].

This work aggressively reduced the power by 1) reducing the baseband signal bandwidth to 300 Hz, suitable for many event-driven applications, to aggressively filter noise; 2) employing a high-Q transformer/filter that passively amplifies the voltage of the incoming RF waveform by 25 dB and filters adjacent channel noise and interferers; 3) simultaneously demodulating and amplifying the wake-up signal via a highimpedance dynamic threshold MOS envelope detector (ED) with subthreshold activeinductor biasing; 4) digitizing the ED output via a regenerative comparator with kickback elimination; 5) generating the baseband clock via a 0.9 pJ/cycle, 1.1 nW relaxation oscillator [25]; 6) decoding the received OOK signal modulated with a custom 16-bit code word using a high-V<sub>t</sub> subthreshold digital baseband correlator; and 7) operating all circuits at 0.4 V to minimize static and dynamic power. When published in 2017, this work reduced the power consumption by over 1,000× from the state of the art. Follow-on work demonstrated that this concept works at higher frequencies (e.g., 400 MHz and 9 GHz); as shown in Figure 9(b), it can have sensitivities better than –100 dBm, and it can be made robust against process, voltage, and temperature (PVT) variation [26], [27], [28].

# IoT: Low-Power MedRadio

The IoT era is experiencing rapid growth with the deployment of a wide variety of sensor nodes, most notably for healthcare monitoring and industrial automation. An important distinction from classic radios is that such IoT nodes only need to wirelessly communicate over short distances, typically ~1–2 meters, to reach a nearby data aggregator (e.g., smartwatch or smartphone). Owing to their autonomous and unobtrusive

**Figure 8.** (a) The ET system comprising a GaN soft-switching buck converter, GaN RF PA, and digital front-end environment. (b) The experimental results (Mitsubishi Electric, Nokia/Bell Labs, and UCSD). PWM: pulse width modulation; DE: drain efficiency; LPF: low-pass filter; BC: buck converter; GMPDPD: generalized memory polynomial digital predistortion.

nature, enabling high deployment lifetimes through ultralow-power (ULP) operation is critical and often achieved through aggressive duty cycling.

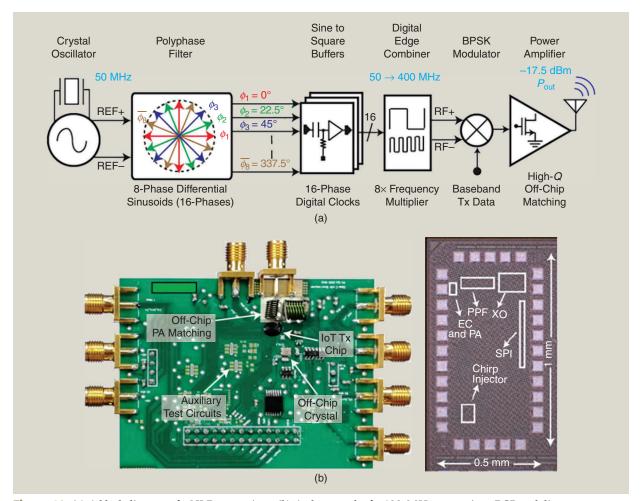

Simplistic transmitter topologies are preferred for this application. In contrast to conventional radios, the PA in a short-range radio is not the highest power-consuming block due to the low output power. Instead, the frequency synthesizer or phase-locked loop (PLL) consumes a significant fraction of the overall transmitter power. The MedRadio/ISM band (~400 MHz) is widely used for the aforementioned applications due to its relatively low carrier frequency and suitability for short distances. To generate this RF carrier in a ULP manner, ring oscillator-based injection-locked clock multipliers with small frequency multiplication factors (~8–12×) are regarded as state of the art [29], [30], [31], [32].

Toward this end, a new technique for PVT-robust, calibration- and regulation-free synthesis of the RF carrier was developed in Prof. Drew Hall's group based on generating poly-phasors at 50 MHz with no power overhead [33]. This is accomplished using a passive polyphase filter directly integrated within a crystal oscillator followed by an 8× edge combiner to synthesize the RF carrier with -109 dBc/Hz phase noise at a 100-kHz offset, as illustrated in Figure 10. A dual-supply, inverse class E PA is implemented for high efficiency at low output power (–17.5 dBm). Openloop operation permits aggressive duty cycling (<40 ns startup time). This work demonstrated a BPSK, PVTrobust transmitter fabricated in 22 nm fully-depleted SOI technology when operated from a 0.4-/0.2-V supply consuming 67 µW with 27% global efficiency. This radio demonstrates excellent robustness to process variation, consistent performance across -30 to 90 °C, and complete insensitivity to voltage variation. This work achieves the best energy efficiency (67 pJ/bit) and lowest power (67 µW) among reported sub-1 mW

narrowband transmitters, significantly advancing the state of the art for low-power, short-range radios.

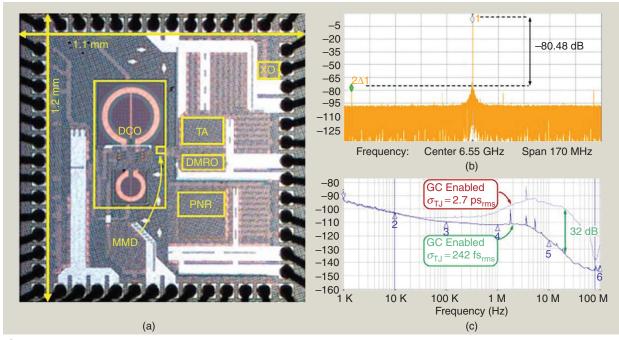

# **Mixed Signal Circuits: Phase-Locked Loops**

The relentless evolution of wireless transceiver standards toward higher bandwidths, higher-order modulation, and higher receive sensitivities imposes increasingly stringent requirements on local oscillator frequency synthesis in terms of rms jitter, spot phase noise, and spurious content. For example, in the 5G NR wireless standard, error vector magnitude requirements for higher than 64 quadrature amplitude modulation require a LO frequency synthesizer with a total rms integrated jitter less than 90 fs, which is very challenging.

The best-performing present-day PLLs are analog PLLs, i.e., PLLs based on conventional analog circuitry, so analog PLLs are the predominant means of frequency synthesis in high-performance commercial wireless transceivers. Unfortunately, analog PLLs require largearea loop filters, are not inherently reconfigurable, and are not amenable to digital calibration. Yet, reconfigurability is essential as modern wireless standards require handling widely variable data rates, and digital calibration is increasingly necessary to address issues associated with the low supply voltages, high device nonlinearity, poor signal isolation, and device leakage of highly scaled CMOS technology nodes as well as for the cancellation of mutual interference among the multiple on-chip PLLs required for carrier aggregation. In contrast, digital PLLs have very small loop filters, are easily reconfigurable, and are amenable to digital calibration, but they have yet to achieve the phase error performance of their analog counterparts [34, and references therein]. To date, the best-performing published digital PLLs are based on analog sampling or digital bang-bang (BB) architectures. However, both types of PLLs have practical issues. Sampling PLLs suffer from

Figure 9. (a) A block diagram of a WuRX. (b) A photograph of a 9-GHz WuRX assembly.

IEEE microwave magazine

poor reference spur performance and high PVT sensitivity because their loop dynamics are highly dependent on the slope of the sampled waveform around its midscale crossings. BB digital PLLs suffer from locking issues under large frequency steps, loop dynamics that depend on the PLL's noise sources, and require impractically high reference frequencies to sufficiently suppress the quantization error introduced by the BB phase detector. Furthermore, the digitally controlled oscillators (DCOs) required in digital PLLs lead to a serious, but rarely acknowledged, intermittent phase noise degradation phenomenon called spectral breathing.

The ongoing digital PLL research performed by Prof. Ian Galton's group aims to develop new techniques that systematically eliminate the limitations of present-day digital PLLs with the objective of elevating their performance to that of the best present-day analog PLLs while retaining the digital PLL benefits. Research results so far include the development of a robust frequency-to-digital converter-based digital PLL architecture, several phase noise and spurious tone reduction techniques based on time amplification

and digital calibration, and a solution to the spectral breathing problem [34], [35], [36], [37], [38], [39]. The group's first-generation 6- to 7-GHz versions of these PLLs, illustrated in Figure 11, achieve 145-fs rms random jitter performance without the abovementioned drawbacks [38], and the next-generation version currently under design is targeting 75-fs rms jitter performance with best-of-class spurious tone performance.

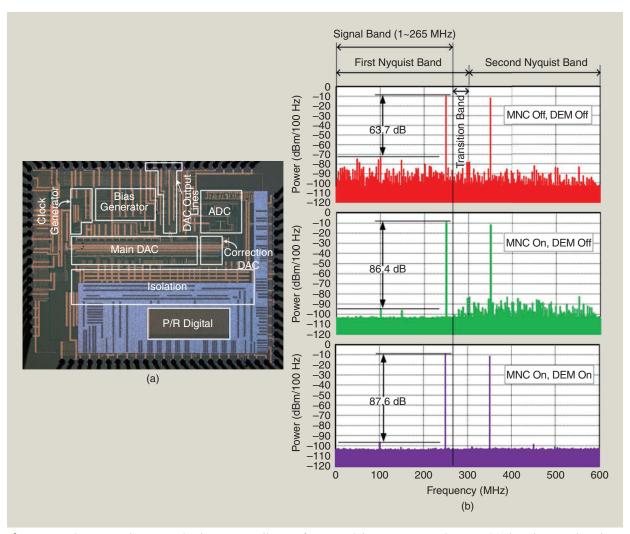

# Mixed Signal Circuits: Digital to Analog Converters

The most significant sources of static and dynamic nonlinear error in practical high-speed, high-resolution, continuous-time RF digital to analog converters (DACs) are clock skew, component mismatches, and intersymbol interference (ISI). Most published digital calibration techniques aimed at addressing these issues only reduce the static portion of such error, which leaves dynamic error as a major limitation. Techniques such as return-to-zero signaling can be used to mitigate ISI, but they generally have undesirable side effects, such as halving the signal power and significantly increasing

Figure 10. (a) A block diagram of a ULP transmitter. (b) A photograph of a 400-MHz transmitter PCB and die.

sensitivity to clock jitter, which greatly increase power consumption and/or decrease signal-to-noise-and-distortion ratio (SNDR). Consequently, clock skew, component mismatches, and ISI typically limit the Nyquist band SNDR of present-day CMOS RF DACs to less than 65 dB. Nonetheless, RF DACs with Nyquist band SNDRs of well over 65 dB are increasingly necessary for high-performance wireless applications such as 5G cellular base station transmitters. The ongoing DAC research performed by Ian Galton's group at UCSD aims to address this disconnect via digital calibration techniques that adaptively measure and cancel both static and dynamic DAC errors from clock skew, component mismatches, and ISI in real time.

The difficulty that has prevented most published DAC calibration techniques from suppressing dynamic error arises from a property inherent to continuous-time DACs. Such DACs generate a continuous-time output pulse for each input codeword, and the output pulse has a bandwidth that far exceeds the DAC's sample rate because its duration is time limited to one clock period. Therefore, any technique that cancels dynamic error either must do so over a bandwidth much wider than the DAC's signal bandwidth, which is unlikely to be practical given the multi-GHz sample rates required of RF DACs, or must perform frequency selective cancellation over a single Nyquist band. Prof. Galton's group recently developed the first technique to accomplish this that does not require elaborate manual

tuning [40]. This mismatch-noise cancellation (MNC) technique cancels static and dynamic errors from clock skew and component mismatches over an RF DAC's first Nyquist band. The initial version of the MNC technique has been used to demonstrate a 600 MS/s DAC IC that achieves a Nyquist band SNDR of 77 dB, as illustrated in Figure 12 [41]. This circuit still has two limitations: it oversamples the DAC output, which limits the sample rate of the DAC IC to 600 MHz, and it does not cancel ISI. The group has since developed a subsampling version of the MNC technique that eliminates the oversampling requirement [42] and a separate technique to address ISI.

# Beam-Steering Ambient Wi-Fi and Bluetooth Signals for ULP IoT Devices

Wireless security cameras, wearable devices, pet health tracking systems, wireless earbuds, augmented reality glasses, and more are all starting to take hold in today's marketplace. However, there is a major problem faced by many of these IoT applications: power consumption. Most of these devices are designed to be small and portable, and yet some of these devices consume so much power that they must be plugged into the wall (e.g., wireless security cameras), or the devices must be so small they do not have room for a large battery, and as a result, their battery life is poor (e.g., wireless earbuds). A key culprit for this is the relatively high power consumption of the radio circuits that enable

**Figure 11.** The digital fractional-N PLL including gain calibration and time amplifier: (a) chip photograph, (b) output spectrum at 6.5 GHz showing low reference spur, and (c) phase noise with and without gain calibration enabled. DCO: digitally controlled oscillator; PNR: place and route; DMRO: dual-mode ring oscillator; TA: time amplifier; XO: crystal oscillator; MMD: multi-modulus divider; GC: gain calibration.

IEEE microwave magazine May 2023

wireless communication. Wi-Fi, and even Bluetooth Low Energy—despite "low energy" being in the name of the standard—often dominate the overall power of such devices, and thus, such devices either require wall power or have a short battery life.

In the groups of Prof. Patrick Mercier and Dinesh Bharadia, work envisions a future where devices like wireless security cameras do not have to be plugged into the wall and can be placed anywhere, or where the battery life of other IoT devices can be 100 times longer. The key to enabling this vision involves not generating the Wi-Fi or Bluetooth signals on the IoT device itself but rather leveraging the fact that smartphones and routers, which either have a large battery or are already plugged into the wall, do a very capable job of generating these signals already. By hitchhiking on top of these existing transmissions, the IoT device can avoid the power consumption of expensive circuits operating at GHz frequencies.

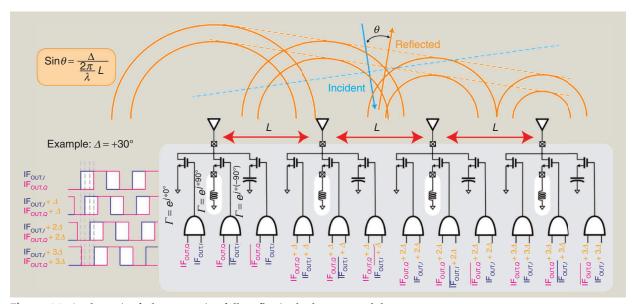

A technique to achieve this is backscatter communication, whereby an incident Wi-Fi or Bluetooth signal arrives at an antenna, and depending on what impedance is loading the antenna on the IoT device, a certain portion of the signal will be reradiated back to the environment. By dynamically controlling what kind of impedance is connected to the antenna, additional data can be modulated on top of the incident signal. While this forms the basis for RFID systems, and some previous work on Wi-Fi backscatter has been demonstrated using discrete parts [43], [44], our recent previous work showed that Wi-Fi communication can be achieved at ~1,000 times lower power than conventional approaches using this technique, a major improvement toward enabling the next-generation IoT vision [45], [46], [47].

The key challenge in backscatter communication, however, is range: since there is no active transmitter on the IoT device, the reradiated signal is weak

**Figure 12.** The 600 MS/s DAC with adaptive cancellation of static and dynamic mismatch errors: (a) chip photograph and (b) one-tone output spectra with and without digital dynamic element matching (DEM) and MNC enabled.

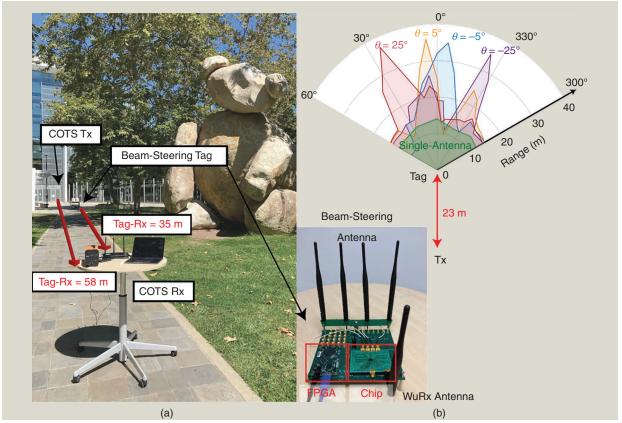

and will only go so far before being lost to noise (e.g., 10 meters in previous work), as shown by the link budget in Figure 13. In fact, due to limitations set by the FCC, standards, or receiver noise constraints, the only way to improve range in backscatter systems is to either improve insertion loss at the tag or add multiple input/multiple output (MIMO) gain. Our most recent work featured improvements on both fronts [48]. For example, we developed a transmission-linefree single-antenna backscatter modulator that enables fully reflective single-side-band QPSK signaling without requiring a power combiner, thereby enabling a low overall insertion loss. Adding MIMO techniques on top of this normally requires precise control of the phase of a multi-GHz signal, which can consume significant amounts of power. In our latest work (Fig-

significant amounts of power. In our latest work (Figure 14), we demonstrated this can be achieved with state of the art. Although the state of the art. Al

**Figure 13.** The link budget constraints in backscatter systems. The only opportunity to improve the range involves improving the insertion loss and adding multiple input/multiple output (MIMO) gain. BW: bandwidth; TX: transmitter; RX: receiver; AP: access point.

MIMO Gain +  $P_{Tx} - PL_1 - IL_{Tag} - PL_2 \ge P_{sens.Rx}$

only microwatts of power by operating at baseband, thereby keeping the ~1,000 times power reduction in place, while increasing the range from 10 to 50+ meters [48] (Figure 15). We also demonstrated techniques to enable backscattering of Bluetooth signals, for an ~100 times power reduction. These results represent a major step forward to making backscatter communication, and as a result small, tetherless IoT devices, a reality.

### **Outlook**

Academic research continues to have a major role in advancing microwave and mm-wave technology for wireless communications. Many academic demonstrations have been rapidly followed by industry. At UCSD, we appreciate that we have had access to a variety of advanced process nodes, which is important to push the state of the art. Although the coverage here is limited to

highlights and short descriptions, interested readers are encouraged to view the attached references or contact the authors for further information.

# **Acknowledgment**

The authors are grateful to their colleagues within UCSD's CWC directed by Prof. Sujit Dey and to the numerous companies that provide support for the center. Partial funding for the work reported here was also provided by a variety of other companies and U.S. government agencies.

for 802.11b Signal (BW = 20 MHz)

**Figure 14.** A schematic of a beam-steering fully reflective backscatter modulator.

ieee microwave magazine

**Figure 15.** A photograph of the test setup, demonstrating a 58-m Wi-Fi access point separation (tag in between) with (a) reliable communication and (b) beam-steering capabilities. COTS: commercial off-the-shelf; FPGA: field-programmable gate array.

### References

- O. Inac, D. Shin, and G. M. Rebeiz, "A phased array RFIC with builtin self-test capabilities," *IEEE Trans. Microw. Theory Techn.*, vol. 60, no. 1, pp. 139–148, Jan. 2012, doi: 10.1109/TMTT.2011.2170704.

- [2] B. Rupakula and G. M. Rebeiz, "Third-order intermodulation effects and system sensitivity degradation in receive-mode 5G phased-arrays in the presence of multiple interferers," *IEEE Trans. Microw. Theory Techn.*, vol. 66, no. 12, pp. 5780–5795, Dec. 2018, doi: 10.1109/TMTT.2018.2854194.

- [3] A. H. Aljuhani, T. Kanar, S. Zihir, and G. M. Rebeiz, "A 256-element Ku-band polarization agile SATCOM transmit phased-array with wide-scan angles, low cross-polarization, deep nulls and 36.5 dBW EIRP per polarization," *IEEE Trans. Microw. Theory Techn.*, vol. 69, no. 5, pp. 2594–2608, May 2021, doi: 10.1109/TMTT.2021.3053293.

- [4] G. Gultepe, T. Kanar, S. Zihir, and G. M. Rebeiz, "A 1024-element Ku-band SATCOM phased-array transmitter with 45-dBW singlepolarization EIRP," *IEEE Trans. Microw. Theory Techn.*, vol. 69, no. 9, pp. 4157–4168, Sep. 2021, doi: 10.1109/TMTT.2021.3075678.

- [5] G. Gultepe, T. Kanar, S. Zihir, and G. M. Rebeiz, "A 256-element dual-beam polarization-agile SATCOM Ku-band phased-array with 5 dB/K G/T," *IEEE Trans. Microw. Theory Techn.*, vol. 69, no. 11, pp. 4986–4994, Nov. 2021, doi: 10.1109/TMTT.2021.3097075.

- [6] S. Li, Z. Zhang, and G. M. Rebeiz, "An eight-element 140-GHz wafer-scale IF beamforming phased-array receiver with 64-QAM operation in CMOS RFSOI," *IEEE J. Solid-State Circuits*, vol. 57, no. 2, pp. 385–399, Feb. 2022, doi: 10.1109/JSSC.2021.3102876.

- [7] K. Low and G. M. Rebeiz, "A 17.7–20.2-GHz 1024-element -band SAT-COM phased-array receiver with 8.1-dB/K G/T, ±70° beam scanning, and high transmit isolation," *IEEE Trans. Microw. Theory Techn.*, vol. 70, no. 3, pp. 1769–1778, Mar. 2022, doi: 10.1109/TMTT.2022.3142275.

- [8] S. Li, Z. Zhang, and G. M. Rebeiz, "An eight-element 136-147 GHz wafer-scale phased-array transmitter with 32 dBm peak EIRP and >16 Gbps 16QAM and 64QAM operation," *IEEE J. Solid-State Circuits*, vol. 57, no. 6, pp. 1635–1648, Jun. 2022, doi: 10.1109/JSSC.2022. 3148385

- [9] O. El-Aassar and G. M. Rebeiz, "A cascaded multi-drive stacked-SOI distributed power amplifier with 23.5 dBm peak output power and over 4.5-THz GBW," *IEEE Trans. Microw. Theory Techn.*, vol. 68, no. 7, pp. 3111–3119, Jul. 2020, doi: 10.1109/TMTT.2020.2984226.

- [10] S. Li and G. M. Rebeiz, "A 130-151 GHz 8-way power amplifier with 16.8-17.5 dBm Psat and 11.7-13.4% PAE using CMOS 45nm RF-SOI," in Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC), 2021, pp. 115–118, doi: 10.1109/RFIC51843.2021.9490507.

- [11] P. Asbeck, S. Alluri, N. Rostomyan, and J. A. Jayamon, "Reliability of CMOS-SOI power amplifiers for millimeter-wave 5G: The case for pMOS," in *Proc. IEEE Int. Rel. Phys. Symp. (IRPS)*, 2022, pp. 4B.1–4B.1-9, doi: 10.1109/IRPS48227.2022.9764417.

- [12] M. Özen, K. Andersson, and C. Fager, "Symmetrical doherty power amplifier with extended efficiency range," *IEEE Trans. Microw. Theory Techn.*, vol. 64, no. 4, pp. 1273–1284, Apr. 2016, doi: 10.1109/TMTT.2016.2529601.

- [13] N. Rostomyan, M. Özen, and P. Asbeck, "28 GHz Doherty power amplifier in CMOS SOI with 28% back-off PAE," IEEE Microw. Wireless Compon. Lett., vol. 28, no. 5, pp. 446–448, May 2018, doi: 10.1109/ LMWC.2018.2813882.

- [14] S. Alluri, N. Rostomyan, and P. Asbeck, "A Ka band 2-stage linear Doherty amplifier with 23dBm Psat and 29% 6dB-backoff PAE in pMOS-SOI," in Proc. IEEE Topical Conf. RF/Microw. Power Amplifiers Radio Wireless Appl. (PAWR), 2021, pp. 52–54, doi: 10.1109/PAWR51852.2021.9375501.

May 2023 IEEE microwave magazine 43

- [15] F. Kimball et al., "High-efficiency envelope-tracking W-CDMA base-station amplifier using GaN HFETs," *IEEE Trans. Microw. Theory Techn.*, vol. 54, no. 11, pp. 3848–3856, Nov. 2006, doi: 10.1109/TMTT.2006.884685.

- [16] F. Wang et al., "Design of wide-bandwidth envelope-tracking power amplifiers for OFDM applications," *IEEE Trans. Microw. Theory Techn.*, vol. 53, no. 4, pp. 1244–1255, Apr. 2005, doi: 10.1109/ TMTT.2005.845716.

- [17] H.-P. Le, S. Sanders, and E. Alon, "Design techniques for fully integrated switched-capacitor DC-DC converters," *IEEE J. Solid-State Circuits*, vol. 46, no. 9, pp. 2120–2131, Sep. 2011, doi: 10.1109/ JSSC.2011.2159054.

- [18] C. Hardy, Y. Ramadass, K. Scoones, and H.-P. Le, "A flying-in-ductor hybrid DC–DC converter for 1-cell and 2-cell smart-cable battery chargers," *IEEE J. Solid-State Circuits*, vol. 54, no. 12, pp. 3292–3305, Dec. 2019, doi: 10.1109/JSSC.2019.2944837.

- [19] H. Pham, R. Das, C. Hardy, D. Kimball, P. Asbeck, and H.-P. Le, "Adjustable 4-level hybrid converter for symbol power tracking in 5G NR," in Proc. IEEE Appl. Power Electron. Conf. Expo. (APEC), Orlando, FL, USA, 2023.

- [20] Y. Komatsuzaki et al., "A high efficiency 3.6-4.0 GHz envelopetracking power amplifier using GaN soft-switching buck-converter," in Proc. IEEE/MTT-S Int. Microw. Symp. - IMS, 2018, pp. 465–468.

- [21] P. P. Mercier and A. P. Chandrakasan, Eds., Ultra-Low-Power Short-Range Radios. Cham, Switzerland: Springer International Publishing, 2015.

- [22] D. Griffith, "Wake-up radio for low-power internet of things applications: An alternative method to coordinate data transfers," IEEE Solid-State Circuits Mag., vol. 11, no. 4, pp. 16–22, Fall 2019, doi: 10.1109/MSSC.2019.2939335.

- [23] P.-H. P. Wang et al., "A near-zero-power wake-up receiver achieving -69-dBm sensitivity," *IEEE J. Solid-State Circuits*, vol. 53, no. 6, pp. 1640–1652, Jun. 2018, doi: 10.1109/JSSC.2018.2815658.

- [24] H. Jiang et al., "24.5 A 4.5nW wake-up radio with -69dBm sensitivity," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2017, pp. 416–417.

- [25] H. Jiang, P.-H. P. Wang, P. P. Mercier, and D. A. Hall, "A 0.4-V 0.93-nW/kHz relaxation oscillator exploiting comparator temperature-dependent delay to achieve 94-ppm/°C stability," *IEEE J. Solid-State Circuits*, vol. 53, no. 10, pp. 3004–3011, Oct. 2018, doi: 10.1109/JSSC.2018.2859834.

- [26] H. Jiang et al., "A 22.3-nW, 4.55 cm2 temperature-robust wake-up receiver achieving a sensitivity of –69.5 dBm at 9 GHz," *IEEE J. Solid-State Circuits*, vol. 55, no. 6, pp. 1530–1541, Jun. 2020, doi: 10.1109/JSSC.2019.2948812.

- [27] P.-H. P. Wang et al., "A 400 MHz 4.5 nW– 63.8 dBm sensitivity wake-up receiver employing an active pseudo-balun envelope detector," in Proc. 43rd IEEE Eur. Solid State Circuits Conf. (ESSCIRC), Sep. 2017, pp. 35–38, doi: 10.1109/ESSCIRC.2017.8094519.

- [28] P.-H. P. Wang et al., "A 6.1-nW wake-up receiver achieving -80.5-dBm sensitivity via a passive pseudo-balun envelope detector," *IEEE Solid-State Circuits Lett.*, vol. 1, no. 5, pp. 134–137, May 2018, doi: 10.1109/LSSC.2018.2875826.

- [29] J. Pandey and B. P. Otis, "A sub-100 W MICS/ISM band transmitter based on injection-locking and frequency multiplication," *IEEE J. Solid-State Circuits*, vol. 46, no. 5, pp. 1049–1058, May 2011, doi: 10.1109/JSSC.2011.2118030.

- [30] X. Liu, M. M. Izad, L. Yao, and C. Heng, "A 13 pJ/bit 900 MHz QPSK/16-QAM band shaped transmitter based on injection locking and digital PA for biomedical applications," *IEEE J. Solid-State Circuits*, vol. 49, no. 11, pp. 2408–2421, Nov. 2014, doi: 10.1109/ JSSC.2014.2354650.

- [31] W. Li, Y. Duan, and J. M. Rabaey, "A 200Mb/s inductively coupled wireless transcranial transceiver achieving 5e-11 BER and 1.5pJ/b transmit energy efficiency," in *Proc. IEEE Int. Solid State Circuits Conf. (ISSCC)*, Feb. 2018, pp. 290–292, doi: 10.1109/ISS-CC.2018.8310298.

- [32] S. Mondal and D. A. Hall, "A107 μW MedRadio injection-locked clock multiplier with a CTAT-biased 126 ppm/°C ring oscillator,"

- in *Proc. IEEE Custom Integr. Circuits Conf. (CICC)*, Apr. 2019, pp. 1–4, doi: 10.1109/CICC.2019.8780130.

- [33] S. Mondal and D. A. Hall, "A 67-µW ultra-low power PVT-robust MedRadio transmitter," in Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC), Aug. 2020, pp. 327–330, doi: 10.1109/RFIC49505.2020.9218405.

- [34] C. Weltin-Wu, G. Zhao, and I. Galton, "A 3.5 GHz digital fractional- PLL frequency synthesizer based on ring oscillator frequency-to-digital conversion," *IEEE J. Solid-State Circuits*, vol. 50, no. 12, pp. 2988–3002, Dec. 2015, doi: 10.1109/JSSC.2015.2468712.

- [35] W. Wu et al., "A 28-nm 75-fs rms analog fractional- N sampling PLL with a highly linear DTC incorporating background DTC gain calibration and reference clock duty cycle correction," *IEEE J. Solid-State Circuits*, vol. 54, no. 5, pp. 1254–1265, May 2019, doi: 10.1109/ ISSC.2019.2899726.

- [36] M. Mercandelli et al., "17.5 A 12.5GHz fractional-N type-I sampling PLL achieving 58fs integrated jitter," in Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC), San Francisco, CA, USA, 2020, pp. 274–276, doi: 10.1109/ISSCC19947.2020.9063135.

- [37] E. Alvarez-Fontecilla, A. I. Eissa, E. Helal, C. Weltin-Wu, and I. Galton, "Delta-sigma FDC enhancements for FDC-based digital fractional-N PLLs," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 68, no. 3, pp. 965–974, Mar. 2021, doi: 10.1109/TCSI.2020.3040346.

- [38] E. Helal, E. Alvarez-Fontecilla, A. I. Eissa, and I. Galton, "A time amplifier assisted frequency-to-digital converter based digital fractional-N PLL," *IEEE J. Solid-State Circuits*, vol. 56, no. 9, pp. 2711– 2723, Sep. 2021, doi: 10.1109/JSSC.2020.3048650.

- [39] E. Alvarez-Fontecilla, E. Helal, A. I. Eissa, and I. Galton, "Spectral breathing and its mitigation in digital fractional-N PLLs," *IEEE J. Solid-State Circuits*, vol. 56, no. 10, pp. 3191–3201, Oct. 2021, doi: 10.1109/JSSC.2021.3074814.

- [40] D. Kong and I. Galton, "Adaptive cancellation of static and dynamic mismatch error in continuous-time DACs," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 65, no. 2, pp. 421–433, Feb. 2018, doi: 10.1109/TCSI.2017.2737986.

- [41] D. Kong, K. Rivas-Rivera, and I. Galton, "A 600 MS/s DAC with over 87dB SFDR and 77dB peak SNDR enabled by adaptive cancellation of static and dynamic mismatch error," *IEEE J. Solid-State Circuits*, vol. 54, no. 8, pp. 2219–2229, Aug. 2019, doi: 10.1109/JSSC.2019.2912338.

- [42] D. Kong and I. Galton, "Subsampling mismatch noise cancellation for high-speed continuous-time DACs," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 66, no. 8, pp. 2843–2853, Aug. 2019, doi: 10.1109/ TCSI.2019.2909173.

- [43] B. Kellogg et al., "Passive Wi-Fi: Bringing low power to Wi-Fi transmissions," in Proc. 13th USENIX Symp. Netw. Syst. Des. Implementation (NSDI), Mar. 2016, pp. 151–164.

- [44] P. Zhang et al., "HitchHike: Practical backscatter using commodity WiFi," in Proc. 14th ACM Conf. Embedded Netw. Sensor Syst. CD-ROM (SenSys), Nov. 2016, pp. 259–271, doi: 10.1145/2994551.2994565.

- [45] P.-H. Wang, C. Zhang, H. Yang, M. Dunna, D. Bharadia, and P. P. Mercier, "A low-power backscatter modulation system communicating across tens of meters with standards-compliant Wi-Fi transceivers," *IEEE J. Solid-State Circuits*, vol. 55, no. 11, pp. 2959–2969, Nov. 2020, doi: 10.1109/JSSC.2020.3023956.

- [46] M. Meng, M. Dunna, H. Yu, S. Kuo, D. Bharadia, and P. P. Mercier, "Improving the range of Wi-Fi backscatter via a passive retro-reflective single-side-band-modulating MIMO array and non-absorbing termination," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2021, pp. 202–204, doi: 10.1109/ISSCC42613.2021.9366014.

- [47] M. Dunna, M. Meng, P.-H. Wang, C. Zhang, P. Mercier, and D. Bharadia, "SyncScatter: Enabling WiFi like synchronization and range for WiFi backscatter communication," in Proc. 18th USENIX Symp. Netw. Syst. Des. Implementation (NSDI), Apr. 2021, pp. 923–937.

- [48] S.-K. Kuo, M. Dunna, D. Bharadia, and P. P. Mercier, "A WiFi and bluetooth backscattering combo chip featuring beam steering via a fully-reflective phased-controlled multi-antenna termination technique enabling operation over 56 meters," in *Proc. IEEE Int.* Solid-State Circuits Conf. (ISSCC), Feb. 2022, pp. 1–3, doi: 10.1109/ISS-CC42614.2022.9731744.