# A 0.4-V 0.93-nW/kHz Relaxation Oscillator Exploiting Comparator Temperature-Dependent Delay to Achieve 94-ppm/°C Stability

Haowei Jiang, *Student Member, IEEE*, Po-Han Peter Wang<sup>®</sup>, *Student Member, IEEE*, Patrick P. Mercier<sup>®</sup>, *Senior Member, IEEE*, and Drew A. Hall<sup>®</sup>, *Member, IEEE*

Abstract—This paper presents the analysis and design of a relaxation oscillator that counteracts the complementary-toabsolute-temperature (CTAT) property of the comparator delay with the proportional-to-absolute-temperature (PTAT) property of the *RC* core to realize temperature-stabilized operation. By using a feedback bias network to linearize the comparator CTAT delay, thus improving the overall temperature stability by 20x, this technique enables a comparator with ~20x less bandwidth and an overall oscillator with ~5x lower power than conventional approaches. In a 0.18- $\mu$ m silicon on insulator CMOS process, this design consumes 1.14 nW from a 0.4-V supply operating at 1.22 kHz, with a temperature coefficient (TC) as low as 40 ppm/°C ( $\mu = 94$  ppm/°C for n = 5) achieving stateof-the-art efficiency (0.93 nW/kHz) for kilohertz-range relaxation oscillators.

*Index Terms*—Internet-of-things (IoT), low power, low voltage, relaxation oscillator, temperature coefficient (TC).

#### I. INTRODUCTION

ISTRIBUTED internet-of-things (IoT) nodes, such as unattended sensors and smart home appliances, are required to operate for long periods of time (e.g., years) from low-volume batteries or energy harvesters [1], [2]. Oscillators are a core block in all IoT nodes used for timers, clocking, and network synchronization. Due to dynamic power limitations and low throughput needs, clock frequencies on the order of a few kilohertz are used in many such applications. Since these oscillators are always on, they must be very low power (e.g.,  $\sim$ nW), compatible with low supply voltages commonly used in IoT nodes (e.g., 0.4 V), and temperature stable to support accurate clocking (i.e.,  $<\pm500$  ppm for the sleep timer of a Bluetooth Low Energy link [1]). Comparator-based relaxation oscillators are a commonly used architecture to generate such kilohertz-range clocks because of their high power efficiency [1], [3].

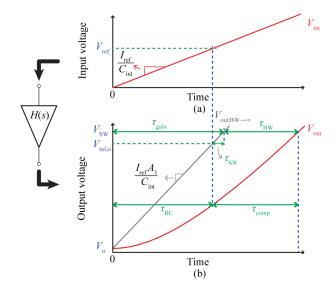

The operation of a comparator-based relaxation oscillator is illustrated in Fig. 1(a). A bias resistor, R, in conjunction with a beta-multiplier is used to set a reference current,  $I_{ref}$ , and a reference voltage,  $V_{ref}$  (=  $RI_{ref}$ ). An integration capacitor,  $C_{int}$ ,

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2018.2859834

$W_{p} \xrightarrow{M_{1} V_{pp} M_{2}} W_{p}$   $W_{N} \xrightarrow{W_{1} V_{pp} M_{2}} U_{ref}$   $W_{N} \xrightarrow{W_{1} V_{pn} M_{4}} V_{ref}$   $M_{3} \xrightarrow{M_{4} V_{ref}} C_{int} \xrightarrow{Digital buffer}$   $W_{n} \xrightarrow{W_{1} V_{ref}} U_{int}$   $W_{n} \xrightarrow{W_{1} V_{ref}} U_{int}$

Fig. 1. (a) Schematic of a typical comparator-based relaxation oscillator. (b) Illustration of delay components, where  $\tau_{buf}$  and  $\tau_{rst}$  are too trivial to show.

is charged by a mirrored version of  $I_{ref}$ , and repeatedly reset by a continuous-time comparator after crossing  $V_{ref}$ , as shown in Fig. 1(b). Thus, the oscillation period,  $T_{OSC}$ , is

$$T_{\rm OSC} = \tau_{\rm RC} + \tau_{\rm comp} + \tau_{\rm buf} + \tau_{\rm rst} \tag{1}$$

where  $\tau_{\rm RC}$  is the time constant formed by R and  $C_{\rm int}$ ,  $\tau_{\rm comp}$ is the comparator delay defined as the time taken to assert the comparator output once  $V_{int}$  exceeds  $V_{ref}$ ,  $\tau_{buf}$  is the digital buffer delay, and  $\tau_{rst}$  is the reset time that includes discharging the capacitor and resetting the comparator, buffer, and switch. Note that resetting the comparator, as will be discussed more in Section III-C, is much faster than  $\tau_{comp}$ . Since the TC of  $\tau_{\rm RC}$  can be accurately controlled (e.g., TC  $\approx$  0) using two trimmed resistors to counteract the TCs of each other [4], [5], and both  $\tau_{buf}$  and  $\tau_{rst}$  are often negligible for kilohertz-range oscillators,  $\tau_{comp}$ , which depends on temperature, becomes significant in the overall temperature stability. Most prior works strived to minimize  $\tau_{comp}$  by increasing the bandwidth, and therefore the comparator power, to make  $\tau_{\rm comp}$  a small fraction of the oscillation period (e.g.,  $\tau_{\rm comp}/T_{\rm OSC}$  < 0.4% in [6]). Other techniques, including feed-forward comparator delay cancellation [4], integrated error feedback [5], and a duty-cycled high-bandwidth comparator [7], have also been used to break this tradeoff. However, they require either redundant comparators or complex digital control logic.

This paper begins by deriving equations for the comparator delay considering the ramp-shaped integration voltage at the comparator input. Based on the analysis, a relaxation oscillator with a two-stage comparator [common gate (CG) stage + common source (CS) stage] is proposed that intentionally utilizes a

0018-9200 © 2018 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

1

Manuscript received September 7, 2017; revised March 22, 2018 and June 27, 2018; accepted July 10, 2018. This paper was approved by Associate Editor Michiel A. P. Pertijs. This work was supported by DARPA under Grant HR0011-15-C-0134. (*Corresponding author: Drew A. Hall.*)

The authors are with the Department of Electrical and Computer Engineering, University of California at San Diego, San Diego, CA 92093 USA (e-mail: drewhall@ucsd.edu).

Fig. 2. Model of the comparator delay following an integrator and driving a buffer. Waveforms at (a) input and (b) output.

proportional-to-absolute-temperature (PTAT) *RC* core, whose delay is counteracted via the linearized complementary-to-absolute-temperature (CTAT) delay of the proposed comparator. Since the comparator delay no longer must be small relative to the clock period, its bandwidth, and therefore power, can be reduced while maintaining temperature stability. The proposed technique has been verified through analysis (Section II), simulations (Section III), and measurement results (Section IV).

## II. COMPARATOR DELAY ANALYSIS

## A. Comparator Delay Model

The comparator input voltage,  $V_{int}$ , is a ramp that can be written as

$$V_{\rm int}(t) = \frac{I_{\rm ref}}{C_{\rm int}} \cdot t \cdot u(t)$$

<sup>(2)</sup>

where u(t) is the unit step function, as shown in Fig. 2(a). The transfer function of the comparator, assuming a single-stage linear, time-invariant continuous-time system, can be written as

$$H(s) = \frac{A_1}{1 + s\tau_1} \tag{3}$$

where  $A_1$  and  $\tau_1$  are the dc gain and time constant of the comparator, respectively. By converting (2) into the s-domain and multiplying by (3), the output behavior of the comparator can be expressed as

$$\Delta V_{\text{out}}(s) = \frac{I_{\text{ref}}}{sC_{\text{int}}}H(s)$$

(4)

where  $\Delta V_{\text{out}}$  is the change in the output voltage. This is graphically illustrated in Fig. 2(b) along with an additional curve corresponding to a comparator with infinite bandwidth  $(V_{\text{out}|BW\to\infty})$  for comparison. Note that both curves start at a voltage  $V_0$  and increase until triggering the buffer and resetting the ramp by reaching  $V_{\text{SW}}$ , which is defined as the switching threshold of the subsequent buffer. Since all of the time

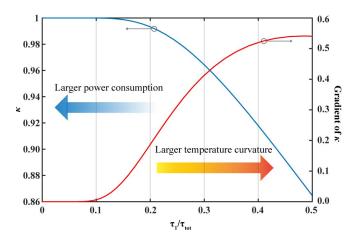

Fig. 3. Numerical solutions for  $\kappa$  versus  $\tau_1/\tau_{tot}$ .

constants are annotated on the output waveform [Fig. 2(b)],  $V_{ref}$  is also referred to the output as  $V_{ref,o}$  for convenience, where  $V_{ref,o}$  is defined as the voltage that the comparator with infinite bandwidth reaches when the inputs are equal (i.e.,  $V_{int} = V_{ref}$ ). The time constants  $\tau_{RC}$  and  $\tau_{comp}$  are annotated in Fig. 2(b) based on the definitions provided in Section I, namely, that  $\tau_{RC}$  ends when  $V_{int}$  crosses  $V_{ref}$  and  $\tau_{comp}$  starts immediately afterward and ends when  $V_{out}$  crosses  $V_{SW}$ .

The infinite bandwidth comparator curve allows one to decouple the effect of finite gain and finite bandwidth, as shown in Fig. 2(b), where  $\tau_{gain}$  is the time taken for  $V_{out|BW\to\infty}$  to cross  $V_{SW}$  and  $\tau_{BW}$  is the remaining time that  $V_{out}$  takes to cross  $V_{SW}$ . The sum of  $\tau_{gain}$  and  $\tau_{BW}$  is the total delay,  $\tau_{tot}$ , which is the time  $V_{out}$  takes to increase from  $V_o$  to  $V_{SW}$ . Note that  $\tau_{tot} \approx T_{OSC}$  [based on (1), just excluding  $\tau_{buf}$  and  $\tau_{rst}$ ]. By substituting  $V_{SW} - V_o$  for  $\Delta V_{out}$  in (4), and taking the inverse Laplace transform, one can derive  $\tau_{tot}$ , and, more importantly  $\tau_{BW}$ , as

$$\tau_{\text{tot}} = \underbrace{\frac{C_{\text{int}}(V_{\text{SW}} - V_{\text{o}})}{I_{\text{ref}}A_{1}}}_{\tau_{\text{gain}}} + \underbrace{\frac{1 - e^{-\frac{\tau_{\text{tot}}}{\tau_{1}}}}{\kappa}}_{\tau_{\text{BW}}} \tau_{1} \tag{5}$$

where  $\kappa$  is a scaling factor bounded between 0 and 1 as shown in Fig. 3. Finally, with  $\tau_{BW} = \kappa \tau_1$  from (5),  $\tau_{comp}$  can be written as

$$\tau_{\rm comp} = \tau_{\rm BW} + \underbrace{(V_{\rm SW} - V_{\rm ref,o}) \frac{C_{\rm int}}{I_{\rm ref}A_1}}_{\tau_{\rm SW}} = \kappa \tau_1 + \tau_{\rm SW} \quad (6)$$

where  $\tau_{SW}$  is the additional time that  $V_{out}$  takes to reach  $V_{SW}$  even with an infinite bandwidth comparator. Note that in practice,  $V_{ref,o} - V_{SW}$  can be either positive or negative. It is also worth pointing out that the underlying assumption of a linear, time-invariant system may not hold for all implementations, especially, considering the large input swing; however, to accurately calculate  $\tau_{SW}$ ,  $A_1$  only needs to be constant over a small range,  $V_{SW} - V_{ref,o}$ , which is easily achieved in practice. This is the motivation for deriving  $\tau_{comp}$  with respect to  $\tau_{SW}$  instead of  $\tau_{gain}$ , which would require  $A_1$  to be linear over the entire range.

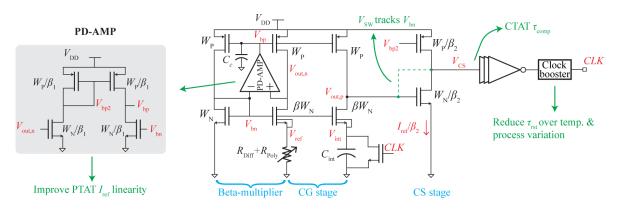

Fig. 4. Schematic of proposed relaxation oscillator employing a two-stage comparator along with PD-AMP in feedback to improve PTAT current temperature linearity.

The key takeaway from this analysis is that the comparator delay consists of two terms: one relating to the finite bandwidth ( $\tau_{BW} = \kappa \tau_1$ ) and another dependent on the following buffer stage switching threshold ( $\tau_{SW}$ ). Rather than trying to minimize  $\tau_{BW}$  to lessen its effect on the oscillator's temperature stability, which would require burning additional power, we propose to compensate it, along with  $\tau_{SW}$ , instead. Section II-B analyzes the temperature dependence of (6), and Section III demonstrates a method to compensate (6) by linearizing  $\kappa \tau_1$  with a PTAT current while canceling  $\tau_{SW}$  with a two-stage comparator.

#### B. Temperature Dependence of the Comparator Delay

To analyze the temperature dependence of  $\tau_{comp}$ , the TC of  $\kappa \tau_1$  and  $\tau_{SW}$  are examined separately to isolate their individual contributions. Assuming operation in subthreshold saturation and neglecting channel length modulation, the current generated by the beta-multiplier in Fig. 1 is

$$I_{\rm ref} = \frac{\ln\left(\beta\right)nk_{\rm B}T}{qR} \tag{7}$$

where  $k_{\rm B}$  is Boltzmann's constant, *n* is the subthreshold slope factor ( $\approx 1.5$  in this process), *q* is the elementary charge,  $\beta$  is the size ratio between  $M_4$  and  $M_3$ , and *T* is the temperature. Thus, (7) is a linear PTAT current. For a comparator biased with  $I_{\rm ref}$ ,  $\tau_1$  is

$$\tau_1 = r_0 C_0 = \frac{V_A C_0}{I_{\text{ref}}} \tag{8}$$

where  $V_A$  is the early voltage, which has minimal temperature dependence [3],  $r_0$  is the output resistance, and  $C_0$  is the load capacitance. Simulation shows that  $C_0$ , which consists of  $C_{db}$  of the transistor and the gate capacitance of the next stage, changes by only 2.2% over the -20 to 70 °C range. By substituting (7) into (8) and taking the partial derivative around room temperature ( $T_0 = 300$  K),  $\tau_1$  has a CTAT dependence with a first-order TC of

$$a_{\tau 1} = -\frac{1}{T_0}.$$

(9)

Since  $\kappa$ , as shown in Fig. 3, is dependent on  $\tau_1$ , it also changes with temperature. If  $\tau_1$  is large,  $\kappa$  is PTAT and

when multiplied by the CTAT  $\tau_1$  results in a negative secondorder TC. Since  $\kappa$  becomes increasingly sensitive to  $\tau_1$  as  $\tau_1$ increases [Fig. 3 (red curve)], the second-order TC of  $\kappa \tau_1$ also becomes significant. Thus, this imposes a design tradeoff where decreasing  $\tau_1$  requires a more power-hungry comparator while increasing  $\tau_1$  relaxes the comparator bandwidth requirement but leads to larger temperature curvature. By designing  $\tau_1/\tau_{tot}$  to be small,  $\kappa$  approaches unity while the gradient of  $\kappa$  with respect to  $\tau_1$  approaches zero. Thus,  $\kappa$  can be approximated as a constant that does not affect the temperature dependence. In summary,  $\kappa \tau_1$  exhibits a CTAT dependence with slightly larger than the first-order curvature that, to the first order, can be counteracted by designing a linear PTAT  $\tau_{RC}$  by trimming *R* to be PTAT.

The TC of  $\tau_{SW}$  depends on two factors:  $C_{\text{int}}/I_{\text{ref}}A_1$  and  $V_{SW} - V_{\text{ref},0}$ . It can be shown that the first term is

$$\frac{C_{\text{int}}}{I_{\text{ref}}A_1} = \frac{C_{\text{int}}}{I_{\text{ref}}g_{\text{m}}r_{\text{o}}} = \frac{C_{\text{int}}}{\ln(\beta)V_{\text{A}}}R$$

(10)

where  $g_m$  is the transconductance. Thus, (10) has the same temperature dependence as *R*. Since  $V_{SW}$  and  $V_{ref,o}$  are determined by the circuit implementation, they are discussed later in Section III. However, the trick is that if the circuit is designed to have  $V_{SW}$  track  $V_{ref,o}$ , then  $\tau_{SW}$  is zero and the temperature dependence does not matter, as shown in (6). In summary, this analysis shows a technique to design a relaxation oscillator by leveraging the CTAT dependence of  $\kappa \tau_1$  while canceling  $\tau_{SW}$ , which deviates from conventional approaches that minimize the entire  $\tau_{comp}/T_{OSC}$  by making the comparator have higher bandwidth.

## III. RELAXATION OSCILLATOR CIRCUIT DESIGN

A 1.2-kHz relaxation oscillator has been designed employing a power efficient comparator with a linear temperature-dependent delay from -20 to 70 °C using the previously-described analysis.

#### A. High Linearity PTAT Reference Generator

The beta-multiplier circuit shown in Fig. 1 is commonly used to generate a PTAT current. To ensure proper operation, each transistor must be in subthreshold saturation

1

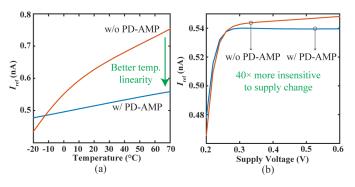

Fig. 5. Simulation results showing (a) reference current versus temperature and (b) reference current versus supply voltage.

$(V_{\text{DSAT}} > 4V_{\text{T}})$ . Changes in the transistor threshold voltage,  $V_{\text{t}}$ , due to temperature and process variation also imposes a limitation on the minimum supply voltage,  $V_{\text{DD,min}}$ . It can be shown that

$$V_{\text{DD,min}} = V_{\text{DSAT,M2}} + V_{\text{DSAT,M4}} + \ln(\beta)V_{\text{T}} + \Delta V_{\text{bp}}$$

$$= [8 + \ln(\beta)]V_{\text{T}} + \frac{\partial V_{\text{bp}}}{\partial T}\Delta T + \frac{\partial V_{\text{bp}}}{\partial V_{\text{t,P}}}\Delta V_{\text{t,P}} \quad (11)$$

where  $\Delta V_{\rm bp}$  is the change in the drain voltage due to both temperature and process variation, and  $\Delta V_{\rm t,P}$  is the change in threshold voltage due to process variation. Thus, a smaller  $\beta$  factor leads to lower  $V_{\rm DD,min}$  where we choose  $\beta = 2$ , resulting in  $R = 47 \text{ M}\Omega$  and  $I_{\rm ref} = 0.54$  nA at room temperature. Compared to  $\beta = 3$  or 4, this saves 17.5 and 30 mV voltage headroom at 70 °C, respectively, but more importantly, a smaller  $\beta$  also leads to a lower R and thus a smaller area.

The sensitivity of  $V_{bp}$  due to temperature and threshold voltage change can be derived from

$$V_{\rm bp} = V_{\rm DD} - nV_{\rm T} \ln\left[\frac{\ln(\beta)n}{(n-1)RK_{\rm P}V_{\rm T}}\right] - |V_{\rm t,P}| \qquad (12)$$

where  $K_{\rm P}$  is the PMOS transistor transconductance parameter inclusive of the sizing. The first-order temperature dependence of  $V_{\rm bp}$  is

$$\frac{\partial V_{\rm bp}}{\partial T} \approx -\frac{nk_{\rm B}}{q} + \frac{\partial |V_{\rm t,P}|}{\partial T} = -0.99 \text{ mV/}^{\circ}\text{C}, \qquad (13)$$

which matches with simulation results (-1.02 mV/°C). Since the total temperature range is 90 °C, the drift in  $V_{bp}$  due to the temperature change is 92 mV [i.e., the second term in (11)]. Furthermore,  $V_{bp}$  changes directly proportional with the threshold voltage deviation due to process variation [i.e.,  $\partial V_{bp}/\partial V_{t,P} = 1$  in (11) accounting for another 45 mV (simulation shows  $\Delta V_{t,P}$  is 45 mV)]. Adding all of these numbers together, the minimum supply voltage should be >363 mV to ensure proper operation. Therefore, we choose a 0.4-V supply. All transistors were carefully sized to ensure  $M_1$  and  $M_4$  are in saturation at the highest temperature (worst case) and Monte Carlo simulations were conducted to check the circuit operation across process variation.

Without compensation,  $I_{ref}$  does not achieve as good of temperature linearity as indicated by (7) due to channel length

modulation and drain-induced barrier lowering. Consequently, this non-linear PTAT current would ruin the linearity of the CTAT comparator delay, thereby degrading the temperature stability. To remedy this, a pseudo-differential amplifier (PD-AMP) that forces the PMOS transistors to have the same VDS was inserted into the bias circuit (Fig. 4). As illustrated in Fig. 5(a), the linearity of  $I_{ref}$  is improved by  $25 \times$  from -20 to 70 °C in simulation. The feedback also improves the  $I_{\rm ref}$  sensitivity to changes in the supply voltage (i.e., power supply rejection ratio), as the change modulates  $V_{\rm DS}$  of each transistor, and therefore the current. Simulation shows  $I_{ref}$ variation reduces from 1% to 0.025% for supply voltages from 0.3 to 0.6 V [Fig. 5(b)]. The PD-AMP is implemented by scaling the original bias circuit by a factor of  $\beta_1$  to ensure the transistors in PD-AMP have the same headroom as the rest of the bias circuit. Since temperature drift is generally slow, the bandwidth requirement for the PD-AMP is greatly relaxed. Thus, we choose  $\beta_1 = 3$  to reduce the power overhead.

### B. Two-Stage $\tau_{SW}$ -Canceling Comparator

The first stage of the comparator is a CG amplifier that reuses part of the reference circuit. This stage does not add any power and, as such, has been widely used [3], [8], [9]; however, it suffers from long and temperature-sensitive delay, especially when the bias current is low. Rather than burning additional power to minimize the comparator delay, the technique described in Section II is applied. Since the *R*-branch and the *C*-branch are matched,  $V_{out,n} = V_{out,p}$  when  $V_{int} = V_{ref}$  assuming infinite bandwidth. Therefore,  $V_{out,n}$ maps to  $V_{ref,o}$  in the model in Section II and  $V_{SW}$  is calculated by shorting the input and output of the buffer stage [10]. If the CG stage feeds into the inverter chain directly, then  $V_{SW}$  is the voltage when the inverter input and output is connected. Assuming *n* is the same for both PMOS and NMOS transistors, the switching point of the inverter is

$$V_{\rm SW,inv} \approx \frac{1}{2} \left[ V_{\rm DD} - n V_{\rm T} \ln \left( \frac{K_{\rm N}}{K_{\rm P}} \right) - |V_{\rm t,P}| + V_{\rm t,N} \right].$$

(14)

Using the same method as in (13), it can be shown that  $V_{\text{out,n}} (\approx V_{\text{bn}})$  only depends on the threshold voltage of the NMOS transistor, which has a CTAT temperature dependence. Thus,  $V_{SW,inv}$  will not track  $V_{out,n}$ , and  $V_{SW,inv} - V_{out,n}$  is PTAT due to  $-|V_{t,P}|$  term in (14). Simulations show that  $V_{\rm SW,inv} - V_{\rm out,n}$  have a strong PTAT temperature dependence (6500 ppm/°C). When setting R to be PTAT,  $\tau_{SW}$  exhibits a significant positive second-order TC due to the cross multiplying between two PTAT terms with large TCs according to (6) and (10). Although  $\kappa \tau_1$  can be designed to be CTAT to counteract the PTAT RC core, therefore, minimizing the firstorder TC of  $T_{OSC}$ , it is the curvature over temperature that cannot be easily compensated. For example, when designing  $\kappa \tau_1 / T_{\rm OSC} = 22\%$ , the strong second-order TC of  $\tau_{\rm comp}$  is only scaled by  $\sim 22\%$  when adding into T<sub>OSC</sub>, and consequently the oscillator can achieve, at best, a temperature stability of  $\sim 28\,800$  ppm (the second-order TC is 12.5 ppm/°C<sup>2</sup>) over the 90 °C range. This simulation is conducted using an ideal resistor with a first-order TC; as such, the non-linearity

JIANG et al.: 0.4-V 0.93-nW/kHz RELAXATION OSCILLATOR EXPLOITING COMPARATOR TEMPERATURE-DEPENDENT DELAY

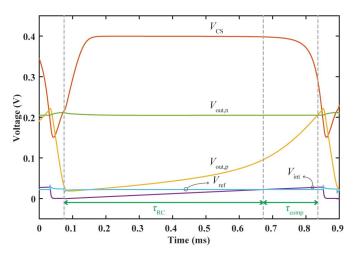

Fig. 6. Simulated waveforms for one oscillation cycle.

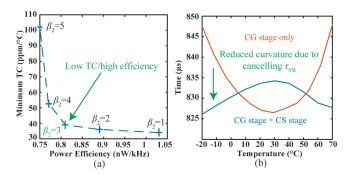

Fig. 7. Simulation results showing (a) TC versus power efficiency for different sizing ratios and (b)  $T_{OSC}$  versus temperature showing curvature.

from the resistor is isolated while examining the comparator temperature dependence. This is why conventionally designs have added more current to minimize  $\kappa \tau_1$ , while using a nearzero TC resistor to mitigate the curvature of  $\tau_{SW}$ . Unfortunately, this is not power efficient and the residue TC (both first- and second-order) of  $\tau_{SW}$  limits the overall temperature stability. Furthermore, more current in the CG amplifier means sourcing more current in all three branches of the circuit, which is very inefficient.

To cancel  $\tau_{SW}$ , a CS stage is added to the existing CG comparator (Fig. 4). As shown in Fig. 6, this CS stage is off during most of a cycle since  $V_{out,p}$  is low. It does not turn on until  $V_{out,p}$  approaches  $V_{out,n}$ . Thus, it behaves more like a dynamic buffer rather than a continuous-time amplifier. The switching voltage,  $V_{SW,CS}$ , is approximately  $V_{out,n}$ , and as such  $V_{SW,CS} - V_{out,n}$ , and consequently  $\tau_{SW}$  is canceled. Since  $V_{bn}$  tracks the NMOS  $V_t$ ,  $\tau_{sw}$  is zero. To ensure good matching, large devices were used and interdigitated in the layout. It should be noted that the PMOS in the CS stage can be biased by either  $V_{bp}$  or  $V_{bp2}$  from the PD-AMP, which is equal to  $V_{bp}$  assuming perfect matching. We used  $V_{bp2}$  for layout convenience. With a canceled  $\tau_{SW}$ , biasing the CG comparator with  $I_{ref}$  results in well-controlled CTAT time constant and thus a CTAT  $\tau_{comp}$ .

Like a current-starved inverter, the delay of the CS stage is inversely proportional to the bias current scale factor  $\beta_2$ . Through proper sizing, we chose  $\beta_2 = 3$  to maintain low power while reducing the temperature stability degradation due

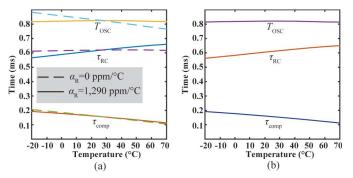

Fig. 8. Simulated delays with (a) ideal resistors and (b) actual RDAC.

to longer  $\tau_{buf}$  and  $\tau_{rst}$  [Fig. 7(a)]. As shown in Fig. 4, including the CS amplifier, the whole buffer chain has four stages to minimize the overall buffer propagation delay  $\tau_{buf}$  (10  $\mu$ s at room temperature) and sharpen the transition edges. The additional CS stage reduces the overall TC curvature by 8× in simulation due to the canceled  $\tau_{SW}$  while still maintaining  $\kappa \tau_1/T_{OSC} = \sim 22\%$  [Fig. 7(b)]. The simulation also shows that the second-order curvature flips after adding the CS stage, which is expected because canceling  $\tau_{SW}$  removes the positive second-order TC of  $\kappa \tau_1$ . A 50-point Monte Carlo simulation with process variation and mismatch showed that the TC varied from 33 to 121 ppm/°C over -20 to 70 °C after calibration—a significant improvement over the ~2000 ppm/°C of the circuit in Fig. 1(a) for the same  $I_{ref}$ .

To illustrate the effectiveness of controlling  $\tau_{\rm comp}$ , two cases were simulated. As shown in Fig. 8(a), when R is set to a zero TC,  $\tau_{\rm RC}$  is constant while  $\tau_{\rm comp}$  is CTAT, and thus  $T_{\text{OSC}}$  is CTAT. When R is set to a positive TC,  $\tau_{\text{RC}}$  becomes PTAT while  $\tau_{comp}$  remains CTAT (but with a smaller TC), and the overall  $T_{OSC}$  is the temperature insensitive. The secondorder TC of  $\tau_{comp}$  degrades from -7.73 to -15.8 ppm/°C<sup>2</sup> after using the PTAT resistor. As a result, the second-order TC of  $T_{OSC}$  degrades from -1.76 to -4.27 ppm/°C<sup>2</sup> accordingly. This is as expected because the non-zero TC of the resistor modulates  $\kappa$  over temperature and creates a secondorder nonlinearity. Note that  $C_{int}$  is ~13 pF, which results in  $\tau_{\rm RC} \approx 610 \ \mu s \ (74\% \ of \ T_{\rm osc})$  at room temperature [Fig. 8(a)],  $au_{

m comp}$  pprox 183  $\mu$ s (22% of  $T_{

m osc}$ ), and the remaining 4% of  $T_{OSC}$  is made up of  $\tau_{buf}$  and  $\tau_{rst}$ , which have little impact on the overall temperature stability. In summary, the additional circuits (PD-AMP and CS stage) increase the power by 34% but improve the temperature stability by  $50 \times$  compared to the original circuit for the same  $I_{ref}$ . Compared to the conventional approach of reducing  $\tau_{\rm comp}/T_{\rm OSC} < 1\%$  with 20× larger  $I_{\rm ref}$ , this technique saves  $\sim 20 \times$  comparator power and  $\sim 5 \times$  total power.

## C. Bias Resistor DAC and Clock Booster

To compensate the CTAT comparator delay, the bias resistor must be trimmed, like other relaxation oscillators that are trimmed to yield zero-TC, though in this case to yield a PTAT *RC* core. All modern CMOS technologies have polysilicon resistors (always PTAT) and diffusion resistors (either PTAT or CTAT, depending on grain size and doping concentration [11]), and thus modern processes support PTAT resistors with adjustable TC,  $\alpha_R$ , via two series PTAT resistors with different TCs (e.g.,  $\alpha_{R1}$  and  $\alpha_{R2}$ ).

Based on (6), with a CG + CS comparator, the oscillation period is

$$T_{\rm OSC} \approx C_{\rm int} R_0 [1 + \alpha_{\rm R} (T - T_0)] + \kappa \tau_1 \tag{15}$$

where  $R_0$  is the resistance of R at room temperature and  $\alpha_R$  is the compound TC of R. By substituting (7) and (8) into the first-order derivative of (15), an optimal  $\alpha_R$  can be calculated as

$$\alpha_{\mathrm{R,opt}} = \frac{V_{\mathrm{A}}C_{\mathrm{CG}}}{\ln\left(2\right)nV_{\mathrm{T0}}C_{\mathrm{int}} + V_{\mathrm{A}}C_{\mathrm{CG}}} \cdot \frac{1}{T_0}$$

(16)

where  $V_{T0}$  is the thermal voltage at  $T_0$  and  $C_{CG}$  is the output capacitance of the CG stage. The  $\alpha_{\rm R,opt}$  was calculated to be  $\sim 1700$  ppm/°C and simulated to be  $\sim 1290$  ppm/°C. The difference comes from the  $\kappa$  variation and first-order TC from  $\tau_{buf}$  and  $\tau_{rst}$ . The nonlinear and time-variant behavior of the comparator also affects the accuracy of calculating  $\alpha_{\rm R,opt}$ . To overcome process variation, the resistor is implemented as a resistor digital-to-analog converter (RDAC) via a series combination of 5-b PTAT and CTAT resistors. The frequency can also be tuned by adjusting both resistors and maintaining the ratio. The oscillator temperature stability was simulated again with the actual RDAC [Fig. 8(b)]. The secondorder nonlinearity (3.99 ppm/°C<sup>2</sup>) of  $T_{OSC}$  is almost the same as the case using an ideal resistor, demonstrating that the second-order TC of the resistor is not an issue in this design.

Since the  $R_{\text{off}}/R_{\text{on}}$  of a MOS switch is small at low supply voltages, a charge pump driven by this oscillator output generates a  $-V_{DD}$  voltage to place the RDAC switches in super cutoff resulting in  $>50 \times$  larger  $R_{\rm off}/R_{\rm on}$  that would otherwise limit the operation range to  $\sim 50$  °C. The discharge switch in parallel with  $C_{int}$  is driven by a modified clock booster [12] to minimize the discharge time and consequently  $\tau_{rst}$  over PVT (Fig. 4). After the capacitor is discharged, the comparator flips and resets the buffer when  $V_{\text{out,p}}$  drops below  $V_{\text{sw,CG}}$ . Thus, there exists a second comparator delay as a part of  $\tau_{rst}$ . Fortunately, the second comparator delay is very short (8  $\mu$ s, <1% of  $T_{OSC}$ ), because first the comparator sees a step Vint this time, instead of a ramp, and second  $V_{out,p}$  only needs to drop a small voltage range to offset the overshoot caused by  $\tau_{buf}$ . Then, the buffer resets and turns off the switch. Simulation shows that  $\tau_{\rm rst}$  is less than 3% of  $T_{\rm OSC}$  with the help of the clock booster.

#### **IV. MEASUREMENT RESULTS**

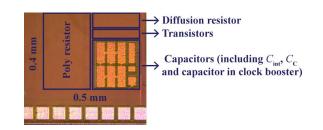

The proposed oscillator was fabricated in a 0.18- $\mu$ m silicon on insulator CMOS process with an active area of 0.2 mm<sup>2</sup> (Fig. 9). Operating at 0.4 V, the power consumption measured at room temperature was 1.14 nW, 70% of which was static power consumed by the reference generator and comparator, with no significant difference between chips (n = 5). The frequency of each chip was tuned to be  $\sim 1220 \pm 15$  Hz. Fig. 10(a) shows the measured frequency of the same oscillator

Fig. 9. Die photograph annotated with components.

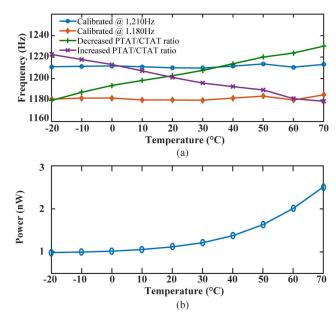

Fig. 10. Measured (a) temperature sensitivity before and after calibration and (b) power versus temperature.

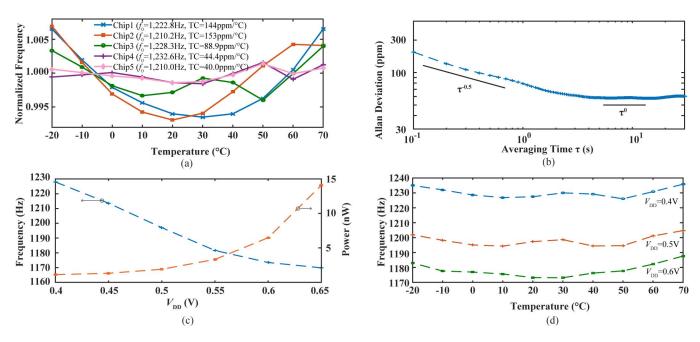

with different RDAC configurations. The TC of the frequency becomes negative when increasing the PTAT/CTAT resistor ratio, and vice versa. By keeping the ratio fixed, the frequency can be tuned with a step size of ~30 Hz. The power when calibrated to 1210 Hz is plotted versus temperature in Fig. 10(b). After a two-point calibration, the measured TC varied from 40–155 ppm/°C (n = 5) over the -20 °C to 70 °C range [Fig. 11(a)]. Due to the process variation, each chip requires separate calibration but both the PTAT and CTAT RDAC configuration codes varied less than six LSBs across all five chips.

Fig. 11(b) shows the Allan deviation plot in an uncontrolled room-temperature environment. The total measurement duration was 300 s, which means each data point was obtained by  $>10\times$  averaging. The short-term uncertainty (jitter) of a relaxation oscillator has been shown to be proportional to the comparator input-referred voltage noise at the switching moment [13]. Thus, the CG comparator with lower bias current inevitably has larger input-referred voltage noise, and therefore larger jitter. This explains why the short-term deviation (e.g., >200 ppm in 0.1 s) is larger than previous works. However, the jitter of such low-power oscillators is typically not an issue in IoT applications because it is used as timer or real-time clock in a wireless network. Thus, long-term stability (Allan deviation floor) is often used to evaluate the

Fig. 11. Measured (a) temperature sensitivity of five chips, (b) Allan deviation, (c) frequency and power versus supply voltage, and (d) temperature sensitivity at different supply voltages.

TABLE I

Performance Comparison of Low-Power, Kilohertz Range Integrated Oscillators

| Parameter                 | [3]       | [4]       | [6]       | [8]         | [9]       | [15]      | [16]      | [17]      | [18]     | This Work |

|---------------------------|-----------|-----------|-----------|-------------|-----------|-----------|-----------|-----------|----------|-----------|

| Technology (nm)           | 180       | 90        | 65        | 350         | 180       | 180       | 250       | 65        | 130      | 180       |

| Frequency (kHz)           | 122       | 100       | 18.5      | 3.3         | 28        | 3         | 6.4       | 33        | 100      | 1.22      |

| Supply (V)                | 0.6       | 0.8       | 1.0       | 1.0         | 1.2       | 0.85      | 0.8       | 1.2       | 1.1      | 0.4       |

| Area (mm <sup>2</sup> )   | 0.03      | 0.12      | 0.032     | 0.1         | 0.16      | 0.5       | 1.08      | 0.015     | 0.25     | 0.2       |

| Allan Dev. Floor (ppm)    | 40        | N/A       | 20        | N/A         | N/A       | 63        | 60        | 4         | N/A      | 58        |

| Temperature Range (°C)    | -20 to 80 | -40 to 90 | -40 to 90 | -20 to 80   | -20 to 80 | -25 to 85 | -20 to 80 | -40 to 90 | 20 to 40 | -20 to 70 |

| Calibration?              | N/A       | N/A       | N/A       | Multi-point | Yes       | N/A       | No        | Yes       | 1-point  | 2-point   |

| TC (ppm/°C)               | 327       | 105       | 38.5      | <500        | 95.5      | 13.8      | 148       | 38.2      | 5        | 94        |

| Power (nW)                | 14.4      | 280       | 120       | 11          | 40        | 4.7       | 75.6      | 190       | 150      | 1.14      |

| Power Efficiency (nW/kHz) | 0.12      | 2.8       | 6.49      | 4.0         | 1.43      | 1.57      | 11.8      | 5.86      | 1.5      | 0.93      |

noise performance. The oscillator required  $\sim 3$  s to reach a 58-ppm floor, which is comparable to previous works.

The oscillation frequency generally does not change with the supply, since both  $\tau_{\rm RC}$  and  $\tau_{\rm comp}$  are independent of supply voltage, to the first order. However, when the comparator is ramping, its V<sub>DS</sub> changes significantly (Fig. 6), and therefore the equivalent  $r_0$  is not constant. When the supply increases, the V<sub>DS</sub> of CG NMOS transistor also increases, resulting in larger  $r_0$  and longer  $\tau_{comp}$ . The measured frequency dropped by 4.3% when the supply was increased from 0.4 to 0.65 V [Fig. 11(c)]. Fortunately, this is not a serious issue when operating under a local regulated supply, which is common in IoT nodes. The power did increase by  $13 \times$  at 0.65 V, mostly from the body leakage currents of the custom inverters with dynamic threshold-voltage MOSFETs [14], since the static bias current is immune to the supply change due to the PD-AMP. No significant difference was observed from different chips. The temperature stability was examined at different supply voltages without recalibration. As shown in Fig. 11(d), the stability is almost unchanged except the center frequency drops when the supply increases. This oscillator achieves

state-of-the-art performance with the lowest power consumption (1.14 nW) at the lowest supply voltage (0.4 V) and the best efficiency (0.93 nW/kHz) among kilohertz-range temperature-compensated relaxation oscillators (Table I).

### V. CONCLUSION

In this paper, the comparator delay and temperature dependence of a relaxation oscillator based on a ramp response model were analyzed. A two-stage  $\tau_{SW}$ -canceling comparator and a technique that utilizes the linear temperature-dependent delay were proposed to implement a relaxation oscillator for low-power and low-voltage applications. Measurement results validate the proposed technique and demonstrate state-of-theart performance.

#### REFERENCES

- D. Griffith, "Synchronization clocks for ultra-low power wireless networks," in *Ultra-Low-Power Short-Range Radios*, P. P. Mercier and A. P. Chandrakasan, Eds. Cham, Switzerland: Springer, 2015, pp. 209–231.

- [2] H. Jiang et al., "A 4.5 nW wake-up radio with -69dBm sensitivity," in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2017, pp. 416–417.

- [3] S. Dai and J. K. Rosenstein, "A 14.4 nW 122 KHz dual-phase currentmode relaxation oscillator for near-zero-power sensors," in *Proc. IEEE Custom Integr. Circuits Conf. (CICC)*, Sep. 2015, pp. 1–4.

- [4] T. Tokairin *et al.*, "A 280 nW, 100 kHz, 1-cycle start-up time, onchip CMOS relaxation oscillator employing a feedforward period control scheme," in *Proc. Symp. VLSI Circuits (VLSIC)*, 2012, pp. 16–17.

- [5] Y.-K. Tsai and L.-H. Lu, "A 51.3-MHz 21.8-ppm/°C CMOS relaxation oscillator with temperature compensation," *IEEE Trans. Circuits Syst.*, *II, Exp. Briefs*, vol. 64, no. 5, pp. 490–494, May 2017.

- [6] A. Paidimarri, D. Griffith, A. Wang, G. Burra, and A. P. Chandrakasan, "An RC oscillator with comparator offset cancellation," *IEEE J. Solid-State Circuits*, vol. 51, no. 8, pp. 1866–1877, Aug. 2016.

- [7] A. Savanth, J. Myers, A. Weddell, D. Flynn, and B. Al-Hashimi, "A 0.68 nW/kHz supply-independent relaxation oscillator with ±0.49%/V and 96 ppm/°C stability," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2017, pp. 96–97.

- [8] U. Denier, "Analysis and design of an ultralow-power CMOS relaxation oscillator," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 57, no. 8, pp. 1973–1982, Aug. 2010.

- [9] Y. H. Chiang and S. I. Liu, "Nanopower CMOS relaxation oscillators with sub-100 ppm/°C temperature coefficient," *IEEE Trans. Circuits Syst.*, *II, Exp. Briefs*, vol. 61, no. 9, pp. 661–665, Sep. 2014.

- [10] B. Razavi, *Design of Analog CMOS Integrated Circuits*, 1st ed. New York, NY, USA: McGraw-Hill, 2001.

- [11] H.-M. Chuang, K.-B. Thei, S.-F. Tsai, and W.-C. Liu, "Temperaturedependent characteristics of polysilicon and diffused resistors," *IEEE Trans. Electron Devices*, vol. 50, no. 5, pp. 1413–1415, May 2003.

- [12] D. C. Daly and A. P. Chandrakasan, "A 6 b 0.2-to-0.9 V highly digital flash ADC with comparator redundancy," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2008, pp. 554–635.

- [13] A. A. Abidi and R. G. Meyer, "Noise in relaxation oscillators," *IEEE J. Solid-State Circuits*, vol. 18, no. 6, pp. 794–802, Dec. 1983.

- [14] F. Assaderaghi, D. Sinitsky, S. A. Parke, J. Bokor, P. K. Ko, and C. Hu, "Dynamic threshold-voltage MOSFET (DTMOS) for ultra-low voltage VLSI," *IEEE Trans. Electron Devices*, vol. 44, no. 3, pp. 414–422, Mar. 1997.

- [15] T. Jang, M. Choi, S. Jeong, S. Bang, D. Sylvester, and D. Blaauw, "A 4.7 nW 13.8ppm/°C self-biased wakeup timer using a switchedresistor scheme," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2016, pp. 102–103.

- [16] H. Wang and P. P. Mercier, "A reference-free capacitive-discharging oscillator architecture consuming 44.4 pW/75.6 nW at 2.8 Hz/6.4 kHz," *IEEE J. Solid-State Circuits*, vol. 51, no. 6, pp. 1423–1435, Jun. 2016.

- [17] D. Griffith, P. T. Røine, J. Murdock, and R. Smith, "A 190 nW 33 kHz RC oscillator with ±0.21% temperature stability and 4 ppm long-term stability," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2014, pp. 300–301.

- [18] A. Shrivastava and B. H. Calhoun, "A 150 nW, 5 ppm/<sup>o</sup>C, 100 kHz on-chip clock source for ultra low power SoCs," in *Proc. IEEE Custom Integr. Circuits Conf.*, Sep. 2012, pp. 1–4.

**Po-Han Peter Wang** (S'16) received the B.S. degree in electrical engineering from National Taiwan University (NTU), Taipei, Taiwan, in 2011, and the M.S. degree in electrical and computer engineering from the University of California at San Diego (UCSD), San Diego, CA, USA, in 2014, where he is currently pursuing the Ph.D. degree.

In 2013, he joined Broadcom Corporation, San Diego, CA, USA, as an RFIC Design Intern. His current research interests include the design of energy-efficient transceiver for wireless communications,

reconfigurable RF front ends and filters, and ultralow-power mixed-signal circuits.

Patrick P. Mercier (S'04–M'12–SM'17) received the B.Sc. degree in electrical and computer engineering from the University of Alberta, Edmonton, AB, Canada, in 2006, and the S.M. and Ph.D. degrees in electrical engineering and computer science from the Massachusetts Institute of Technology (MIT), Cambridge, MA, USA, in 2008 and 2012, respectively.

He is currently an Associate Professor in electrical and computer engineering with the University of California at San Diego (UCSD), San Diego, CA, USA, where he is also the Co-Director of the Center

for Wearable Sensors. His current research interests include the design of energy-efficient microsystems, focusing on the design of RF circuits, power converters, and sensor interfaces for miniaturized systems and biomedical applications.

Dr. Mercier has been a member of the ISSCC International Technical Program Committee (Technology Directions Sub-Committee) and the CICC Technical Program Committee since 2017. He was a recipient of the Natural Sciences and Engineering Council of Canada (NSERC) Julie Payette Fellowship in 2006, the NSERC Postgraduate Scholarships in 2007 and 2009, the Intel Ph.D. Fellowship in 2009, the 2009 IEEE International Solid-State Circuits Conference (ISSCC) Jack Kilby Award for Outstanding Student Paper at ISSCC 2010, the Graduate Teaching Award in Electrical and Computer Engineering at UCSD in 2013, the Hellman Fellowship Award in 2014, the Beckman Young Investigator Award in 2015, the DARPA Young Faculty Award in 2015, the UC San Diego Academic Senate Distinguished Teaching Award in 2016, the Biocom Catalyst Award in 2017, and the NSF CAREER Award in 2018. He has served as an Associate Editor for the IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION from 2015 to 2017. Since 2013, he has been an Associate Editor of the IEEE TRANSACTIONS ON BIOMEDICAL INTEGRATED CIRCUITS and the IEEE SOLID-STATE CIRCUITS LETTERS since 2017. He was the Co-Editor of Ultralow-Power Short Range Radios (Springer, 2015) and Power Management Integrated Circuits (CRC Press, 2016).

**Drew A. Hall** (S'07–M'12) received the B.S. degree (Hons.) in computer engineering from the University of Nevada, Las Vegas, NV, USA, in 2005, and the M.S. and Ph.D. degrees in electrical engineering from Stanford University, Stanford, CA, USA, in 2008 and 2012, respectively.

From 2011 to 2013, he was a Research Scientist with the Integrated Biosensors Laboratory, Intel Corporation, Santa Clara, CA, USA. Since 2013, he has been with the Department of Electrical and Computer Engineering, University of California at

San Diego, San Diego, CA, USA where he is currently an Associate Professor. His current research interests include bioelectronics, biosensors, analog circuit design, medical electronics, and sensor interfaces.

Dr. Hall has been an Associate Editor of the IEEE TRANSACTIONS ON BIOMEDICAL INTEGRATED CIRCUITS since 2015 and a member of the CICC Technical Program Committee since 2017. He was a recipient of the First Place in the Inaugural International IEEE Change the World Competition, the First Place in the BME-IDEA invention competition, both in 2009, the Analog Devices Outstanding Designer Award in 2011, the Undergraduate Teaching Award in 2014, the Hellman Fellowship Award in 2014, and the NSF CAREER Award in 2015. He is a Tau Beta Pi Fellow.

Haowei Jiang (S'15) received the B.S. degree in electrical engineering from the Huazhong University of Science and Technology (HUST), Wuhan, China, in 2014, and the M.S. degree in electrical and computer engineering from the University of California at San Diego (UCSD), San Diego, CA, USA, where he is currently pursuing the Ph.D. degree.

His current research interests include low-power integrated analog/mixed-signal circuit design for sensing systems and biomedical devices.